# 4H-SiC Epitaxial Layers Grown on on-axis Si-face Substrate

<u>J. Hassan</u><sup>a</sup>, J.P. Bergman<sup>a,b</sup>, A. Henry<sup>a</sup>, H.Pedersen<sup>a</sup>, P.J. McNally<sup>c</sup> and E. Janzén<sup>a</sup>

<sup>a</sup> Department of Physics, Chemistry and Biology, IFM Linköping University, S-58183 Linköping, Sweden

<sup>b</sup> Norstel AB, Ramshällsvägen 15, S-60116 Norrköping, Sweden

<sup>c</sup>Nanomaterials Processing Laboratory, Research Institute for Networks & Communications Engineering (RINCE), School of Electronic Engineering, Dublin City University, Dublin 9, Ireland

Tel: +46 13 28 23 80, Fax: +46 13 14 23 37, Email: jawul@ifm.liu.se

Keywords: Chemical vapor deposition, On-axis, X-ray topography, AFM, 4H-SiC, SWBXT

#### Abstract

We report on the growth of 4H-SiC epitaxial layer on 2" full wafer Si-face polished nominally on-axis substrates, using Hot-Wall epitaxy. The polytype stability has been maintained over the larger part of the wafer, but 3C inclusions have not been possible to avoid. Special attention has given to the mechanism of generation and propagation of 3C polytype in 4H-SiC epilayer. Different optical and structural techniques were used to characterize the material and to understand the growth mechanisms. It was found that all 3C inclusions were generated at the interface between the substrate and the epitaxial layer, and no 3C inclusions were initiated at later stages of the growth.

#### Introduction

In high power electronic applications 4H-SiC, due to its wider band gap, high breakdown electric field and high thermal conductivity, has proven to be a superior semiconductor material as compared to conventional semiconductor materials like Si and GaAs [1]. The availability of increasing diameter of single crystal 4H-SiC wafer has opened up the possibilities for many power applications in recent years. The (00.1) Si-face polished, off-cut (4° or 8°) substrates are normally used to grow active layer for SiC electronic devices. With the increasing wafer diameter this offangle results in material losses when wafers are sliced from a boule [2]. Epitaxial layer grown on off-cut wafer on one hand easily replicates the polytype of the substrate, but on other hand makes it possible for basal plane dislocations to penetrate into the epilayer from off-cut substrate. It has reported before that after long operation of bipolar electronic devices under heavy load basal plane dislocations in the epilayer dissociate into two partials, one stationary and one moving thus result in the formation of stacking faults which ultimately degrade forward voltage [3]. The replication of basal plan dislocations into epilayer can be avoided through growth on on-axis substrate. One of the major issue with on-axis growth on (00.1) Si-face is the nucleation of 3C-SiC inclusions which reduces the effective useable area on full wafer for device purpose [4]. Therefore, it is crucial to investigate the origin and propagation of 3C-SiC on 4H-SiC on-axis substrate.

## **Experimental**

A horizontal hot-wall CVD reactor [5] was used for the growth of n-type low doped, thick epilayers on Si-face on-axis substrate. The growth temperature and pressure were 1560 °C and 200 mbar, respectively. Hydrogen purified through heated palladium membrane was used as carrier gas while silane and propane were used as the sources for Si and C, while C/Si=1. Nitrogen was used as n-type dopent. *In situ* high temperature treatment was performed on all samples for 10 minutes in a mixture of hydrogen and propane before growth. In order to reveal 3C parts in the epilayer different methods like molten KOH etching, high resolution X-ray diffraction (HRXRD) and illumination of epilayer under UV laser light at 77K was performed. Surface morphology was observed under optical microscope with Nomarski interface contrast while the surface roughness was measured with tapping mode atomic force microscopy (AFM). Minority carrier lifetime mapping was

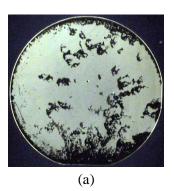

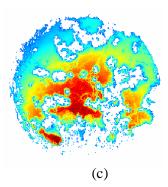

Fig. 1 Full wafer images of thick 4H on-axis grown epitaxial layer. a) Image taken with UV light illumination at 77K. The black areas correspond to 3C-SiC while the rest is 4H-SiC. b) X-ray topographic map of full wafer taken with in-house facility. The black areas are 3C while gray areas are 4H-SiC. C) Carrier life time map at room temperature. White spots are 3C while the rest is 4H-SiC.

performed on full wafer at room temperature. Synchrotron white beam X-ray topography (SWBXT) was performed with the synchrotron radiation from the bending magnet source of the DORIS III storage ring at HASYLAB-DESY, in Hamburg. SWBXT was made in back reflection mode on some selected areas of the sample while full wafer maps were recorded using a Bede Lang X-ray topograph. In order to observe the lateral expansion of 3C nuclei, wafer was cut around 3C inclusion and polished from both sides to reach the area on substrate where 3C nucleation had started at substrate/epi interface. Also a part of wafer with 3C inclusions in it was then polished from epilayer side in steps of  $20\mu m$  and images were recorded with optical microscope after each step.

### **Results and Discussion**

A typical result from an epitaxial growth on on-axis substrate is shown in Fig. 1. The figure shows a full wafer mapping using different experimental techniques. Image taken with UV illumination at 77K is shown in Fig.1a where black areas are related to 3C inclusions while the remaining part is 4H-SiC. Fig. 1b shows a X-ray topographic image of full wafer where black area corresponds to 3C parts while gray area is 4H-SiC. Figure 1c, shows a mapping of the photoluminescence decay time at room temperature. The white areas correspond to the 3C inclusions where no optical signal at the 4H band gap is present. The presence of 3C polytype inclusions in 4H were further confirmed with

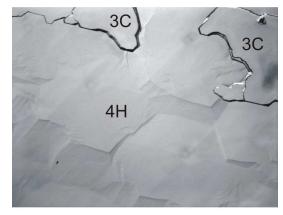

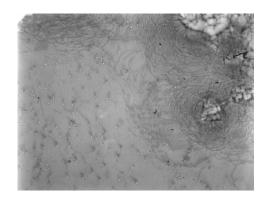

HRXRD. 3C inclusions spread randomly on the wafer with typically higher density at the edges of the wafer which could be due to bad crystal quality of the wafer at edges and rougher surface because of polishing scratches. The surface morphology of epilayer observed under optical microscope shows that 4H parts grew in columns while 3C parts are more flat as shown in Fig. 2. Screw dislocations are the main nucleation center where growth occurs through the spiral growth mechanism. The spiral wounds and forms a pyramid structure around dislocation. This columnar growth of 4H parts could be due to low ad-atom mobility which results in slow lateral growth and hence macro step bunching. 3C inclusion formation on 4H substrate strongly depends on the face polarity with high density of 3C on Si face and almost no 3C on C

Fig. 2 Optical image taken from as grown epilayer showing 3C inclusions in 4H-SiC. 3C parts are more flat as compared to 4H parts.

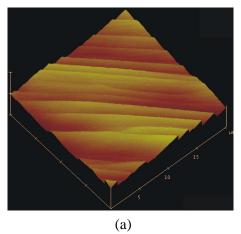

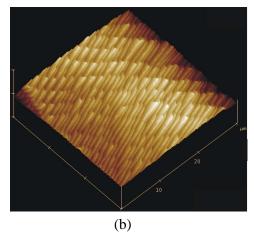

Fig. 3 a)  $20x20 \mu m$  AFM image taken from 3C part. Step height ranging from one bilayer to a few bilayers while RMS is 2nm b)  $20x20 \mu m$  AFM image taken from 4H part. Step height is unit c while RMS is 0.8nm

face which could be due to different surface free energy with high surface free energy on Si face. In order to reduce surface free energy step bunching (hills and valleys) occurs which results in rougher surface. Local growth front destabilization due to local suppression of step-flow mode on substrate imperfections also causes step bunching and results in small (0001) facets. On such facets 3D nucleation of 3C is radically favored. In many cases flat terraces with dimensions of several hundred  $\mu m$  (which is much larger than the diffusion length of ad-atoms) due to step bunching have seen without any 3C nucleation on it. This clearly shows that the growth conditions used are not favorable to start 3D nucleation of 3C on flat terraces. Same could be true at the beginning of the growth and 3C nucleated not through 3D nucleation but due to bad preparation of the surface.

The surface morphology of 4H and 3C-SiC parts was studied by AFM in tapping mode. Fig. 3a shows the AFM image taken on 3C part. The surface roughness over  $20x20~\mu m$  area is 2nm and step height is not uniform ranging from one bilayer to a few of bilayers. Fig. 3b presents  $20x20~\mu m$  scan over 4 H parts where the surface roughness is 0.8 nm and the step height is unit cell height c. The step height is more uniform close to the center of the spiral while it gets worst away from the center of spiral because of step bunching.

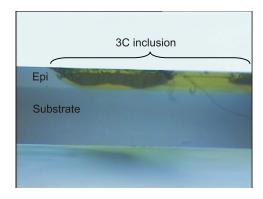

Growth has been made on both as polished and on KOH etched wafer, without any significant difference. The KOH etched wafers also revealed the presence of dislocations, and it was found that there was less probability for 3C nucleation in the areas with high dislocation density (excluding grain boundaries), probably due to the reason that more steps and kinks are available in that area and the distance between two growth centers is less than the ad-atom diffusion length. In order to observe the lateral expansion of 3C nuclei, the wafer was cleaved and polished from both sides to reach the area on the substrate where 3C nucleation had started, as shown in Fig. 4. Optical images taken from the part of wafer polished from epilayer side in steps of 20µm showed that 3C inclusions started at the epilayer-substrate interface at the beginning of the growth run and expanded laterally. It also uncovered some 4H parts in 3C patches which were over grown by 3C during growth. No 3C inclusions were found that started at later stages during the growth. A particular attention has focused to the areas in the epilayer where two spirals meet. No 3C is seen to be nucleated in those areas. The 3C parts, nucleated at the substrate surface seem to propagate laterally between these spirals. Also no 3C parts were seen to originate from micropipes and no disturbance of the surface morphology or other epilayer defects related to micropipes, like half moon and wavy pits, were observed in the vicinity of micropipe as seen in the case of off-axis substrate. This could be due to different growth mechanism in case of on-axis substrate as compared to off-axis substrate.

Fig. 4 Optical image of the cross-section of wafer showing 3C-4H interface and lateral expansion of 3C-SiC.

Fig. 5 SWBXT image taken in back reflection mode. White spots correspond to 3C-SiC. Networks of black lines around 3C are basal plan dislocations.

From a comparison of the full wafer mappings in Fig. 1 it can be seen that the measured reduction in carrier lifetime extends further than the actual presence of 3C inclusions. In order to reveal the nature of defects synchrotron white beam x-ray topography (SWBXT) was performed at the interface of 3C and 4H-SiC on some selected areas on epilayer. Fig. 5 shows SWBXT image taken in back reflection mode. Big white spots on the right top corner are 3C inclusions which are surrounded by a network dislocation lines in the 4H region. These appear with high density at the interface between the 3C and 4H-SiC and were generated during growth in order to compensate the lattice mismatch between the two polytypes. The high dislocation density in the 4H region around 3C inclusions reduces the measured carrier lifetime.

#### **Conclusions**

The growth of 4H SiC epitaxial layers on nominally on-axis substrates has been studied. The polytype stability has been maintained over the larger part of the wafer, but 3C inclusions have not been possible to avoid. The 3C inclusions start only at the beginning of the growth and expand laterally without following any particular direction, probably originating from surface damages and not trough 3D nucleation. KOH etched wafer revealed that there is a less probability for 3C nucleation in the area with high dislocation density, also micropipe did not give rise to the nucleation of 3C. Closely spaced 4H growth spirals did not produce any growth disturbance or 3C inclusions. High density of basal plan misfit dislocation at the interface between 3C and 4H regions caused lower crystal quality as observed through a reduced carrier lifetime around 3C regions.

#### Acknowledgements

This work was supported by the Swedish Research Council and Norstel AB via the project "Industrialization of SiC Material" funded by Vinnova and the Swedish Energy Agency.

#### References

- [1] K.Shenai, R. S. Scott and B. J. Baliga: IEEE Transactions on Elctron Devices, vol. 36, no. 9, September 1998, p. 1811.

- [2] M.Treu, R. Rupp, H. Brunner, F. Dahlquist and Ch. Hecht: Materials Science Forum Vols. 457-460 (2004) p. 981.

- [3] Jacobson, H.; Bergman, J.P.; Hallin, C.; Janzen, E.; Tuomi, T.; Lendenmann, H.: Journal of Applied Physics, v 95, n 3, 1 Feb. 2004, p 1485.

- [4] C. Hallin, I. Ivanov, J. P. Bergman, E. Janzén: Materials Science Forum, 457- 460, (2003) p.193.

- [5] O. Kordina, A. Henry, J. P. Bergman, N. T. Son, W. M. Chen, C. Hallin, and E. Janzén: Applied Physics Letters, v 66, n 11, 13 March 1995, p.1373.

- [6] T. Kimoto and H. Matsunami: J. Appl. Phys. 78 (1995) p. 3132.