Innovative Particle and Radiation Detectors 2023 (IPRD23) 25-29 September 2023 Siena, Italy

# Pixel detector hybridization and integration with anisotropic conductive adhesives

Alexander Volker, a,1 Janis Viktor Schmidt, a Dominik Dannheim, a Peter Svihra, a Mateus Vicente Barreto Pinto, a Rui de Oliveira, a Justus Braach, a Xiao Yang, a Marie Ruat, a Débora Magalhaes, a Matteo Centis Vignali, a Giovanni Calderini, a Helge Kristiansen, a

a CERN,

Meyrin, Switzerland

<sup>b</sup>Universite de Geneve,

Geneva, Switzerland

<sup>c</sup>ESRF,

Grenoble, France

$^{d}FBK$ ,

Trento, Italy

<sup>e</sup>LPNHE,

Paris, France

<sup>f</sup> Conpart AS,

Skjetten, Norway

g DESY,

Hamburg, Germany

E-mail: alexander.volker@cern.ch

<sup>&</sup>lt;sup>1</sup>Corresponding author.

ABSTRACT: A reliable and cost-effective interconnect technology is required for the development of hybrid pixel detectors. The interconnect technology needs to be adapted for the pitch and die sizes of the respective applications. For small-scale applications and during the ASIC and sensor development phase, interconnect technologies must also be suitable for the assembly of single-dies typically available from Multi-Project-Wafer submissions. Within the CERN EP R&D program and the AIDAinnova collaboration, innovative and scalable hybridization concepts are under development for pixel-detector applications in future colliders. This contribution presents recent results of a newly developed in-house single-die interconnection process based on Anisotropic Conductive Adhesives (ACA). The ACA interconnect technology replaces solder bumps with conductive micro-particles embedded in an epoxy layer applied as either film or paste. The electro-mechanical connection between the sensor and ASIC is achieved via thermocompression of the ACA using a flip-chip device bonder. The ACA technology can also be used for ASIC-PCB/FPC integration, replacing wire bonding or large-pitch solder bumping techniques. A specific pixel-pad topology is required to enable the connection via micro-particles and create cavities into which excess epoxy can flow. This pixel-pad topology is achieved with an in-house Electroless Nickel Immersion Gold process that is also under development within the project. The ENIG and ACA processes are qualified with a variety of different ASICs, sensors, and dedicated interconnect test structures, with pad diameters ranging from 12  $\mu$ m to 140  $\mu$ m and pitches between 20  $\mu$ m and 1.3 mm. The produced assemblies are characterized electrically, with radioactive-source exposures, and in tests with high-momentum particle beams. This contribution introduces the developed interconnect and plating processes and showcases different hybrid assemblies produced and tested with the above-mentioned methods. A focus is placed on recent optimization of the plating and interconnect processes, resulting in an improved plating uniformity and interconnect yield.

Keywords: Hybrid detectors, Detector design and construction technologies and materials, X-ray detectors, Timing detectors

## **Contents**

| 1 | Intr | roduction              | 1  |  |

|---|------|------------------------|----|--|

| 2 | Elec | ctroless Plating       | 2  |  |

| 3 | Bon  | 4                      |    |  |

|   | 3.1  | ACA materials          | 4  |  |

|   | 3.2  | Flip-chip bonding      | 4  |  |

| 4 | Res  | 6                      |    |  |

|   | 4.1  | ENIG plating           | 6  |  |

|   | 4.2  | Test-Structure Bonding | 6  |  |

|   | 4.3  | LGAD Hybridisation     | 7  |  |

|   | 4.4  | SPHIRD Hybridisation   | 8  |  |

|   | 4.5  | Timepix3 Hybridisation | 9  |  |

| 5 | Con  | nclusions              | 9  |  |

| 6 | Out  | dook                   | 10 |  |

|   |      |                        |    |  |

#### 1 Introduction

Interconnect technologies from fine pitch hybridization to large pitch module packaging are important for a wide range of applications in the field of high-energy physics and other silicon pixel-detector applications. In many cases state of the art is solder bump bonding in which the electrical connection between metallized pads is created by solder balls under reflow conditions. This requires many steps of preparation including a process called Under Bump Metallization (UBM) which are done on a wafer level prior to dicing. For multi project wafers as they are common in detector R&D these wafer level processes are either not possible or too costly for the scale of the project. Out of this issue arises a need for cost effective single die processing with a fast turn-around time. An innovative approach for in-house single die bonding is discussed in this contribution. The electrical interconnection is created using Anisotropic Conductive Adhesives (ACA) in the form of conductive particles embedded in an epoxy paste or film and by thermo-compressing the adhesive. Commercial use of these types of adhesives can be found in display panel integration[1] and also increasingly in chip-to-film and chip-to-flex bonding[3, 4]. The required surface properties of the devices bonded with ACA are achieved with an in-house single-die plating process.

## 2 Electroless Plating

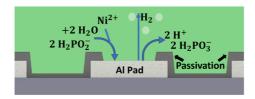

For the topology requirement needed to bond with the ACA, Electroless Nickel Immersion Gold (ENIG) plating is utilized, a method typically used in PCB production[5]. It is a chemical plating process that grows nickel on metallized pads without the need for an external electrical current, making it thereby use able for technologies operating on semiconductor electronics. In the case of ASICs and sensors, the pad metallization widely used is an aluminium alloy which first requires a pre-treatment of the pads in order for the ENIG plating to create a catalytic surface on which the reaction can start reliably. The first step after mounting the samples on a holder is plasma cleaning them. This removes part of the thin oxide layer and increases the wettability for further chemical processing. In the next step the oxide layer is chemically removed and more roughened surface for plating to adhere to is created. The next step is generally referred to as zincation. In this step a thin seed layer of Zinc is chemically deposited on the aluminium surface. The cycling of this step twice or thrice can increase the quality of the zinc seed layer. The sample can now be submerged in the Electroless Nickel bath containing hypophosphite and Ni-Ions to start the plating process as shown in Figure 1. Due to the auto catalytic nature of the process the nickel will grow radially outwards from all points of deposition, thereby creating a mushroom-like shape with increasing plating height.

$$H_2PO_2^- + Ni^{2+} + 2H_2O \rightarrow H_2PO_3^- + H_2 + 2H^+ + Ni^0$$

(2.1)

**Figure 1**. The graphic shows the simplified chemical process in the Electroless Plating bath when plating nickel on aluminium pads partially covered by a passivation layer.

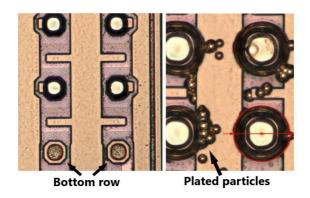

The plating height is controlled by the plating time while defects in the plating growth process limit the height at which uniform growth on all pads can be achieved. Defects observed are single pads not plated or skipped, pads near edges of the chip un-plated or considerably lower plating height. Observations show a plate out effect showing nucleation of nickel plating on surfaces where plating is undesired (see Figure 2 right). This occurs more frequently when the plating gets high enough for the space between pads to shrink considerably. It starts a chain reaction creating increasingly more nucleation spots that each grow with further plating time. A lead-based stabilizer is used as catalyst poison in order to inhibit the plate out. Another challenge to achieve an even plating topology are pads with different metal structures and shorts. These pads can show different plating speeds compared to the rest of the pixel matrix leading to uneven topologies (see Figure 2 left).

After the Electroless Nickel process an Immersion Gold process is used to create a thin gold layer on the previously plated nickel in order to protect them from corrosive conditions. The gold

**Figure 2.** Electroless Nickel defects on small pitch  $(55 \mu m)$  devices. The left picture shows a electrically connected row of pads in the bottom of the pixel matrix. This row shows frequently different plating behaviour compared to the rest of the pixel matrix. The right picture shows plate out happening between pads. Small dots that increase in number and grow leading to shorts.

atoms replace the nickel atoms at the surface, slowly growing the gold layer. The chemical equation for this process is shown in 2.2.

$$Ni + 2Au^+ \rightarrow Ni^{2+} + 2Au$$

(2.2)

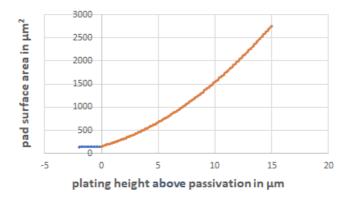

**Figure 3**. Graph showing the calculated increase of Ni-pad surface with increased plating height assuming uniform radial growth. The initial Al-pad is  $14\mu$ m in diameter and  $2\mu$ m in height below the passivation layer.

Agitation of the Electroless Nickel bath is an important parameter to control as it strongly affects the diffusion zone in which the chemical processes of the plating take place[6]. A stirring hotplate setup is used where the stirring speed is adjusted according to the surface of the growing nickel bumps  $\omega \sim r(r+1)$ . Due to the mentioned mushroom-like shape the surface area will grow quickly for small pad devices as shown in Figure 3. All measures of plating height are stated with reference to the passivation covering the edges of the pads. Adjusting the stirring results in more uniform topologies needed for higher interconnection yields.

# 3 Bonding with Anisotropic Conductive Adhesives

#### 3.1 ACA materials

While the Anisotropic Conductive Films (ACF) are commercial products with detailed bonding parameters (see Table 1), adjustments based on material and pixel pad layout still have to be done. This can be the case for large chips where it is required to squeeze out as much of the epoxy as possible prior to curing the epoxy. For the Anisotropic Conductive Paste (ACP), commercial epoxies with different conductive particles embedded are available for use based on material characteristics such as viscocity and radiation hardness needed for the device and bonding process. Mixing the conductive particles into the paste is also done in-house. In use are a range of particles in sizes and coating materials as shown in Table 1.

| ACF                           | 1     | 2     | 3                       | 4     | 5               |

|-------------------------------|-------|-------|-------------------------|-------|-----------------|

| Part. diameter<br>[μm]        | 3     | 3     | 3.5                     | 10    | 3.2             |

| Thickness [μm]                | 18    | 14    | 16                      | 50    | 18              |

| Particle density<br>[pcs/mm²] | 71k   | 60k   | 23k                     | 1     | 28k             |

| Pressure [MPa]                | 30-80 | 50-90 | 40-90                   | 30-50 | 40-80           |

| Aligned                       | no    | no    | Particles at same depth | no    | surface<br>grid |

| Sheet or reel                 | sheet | reel  | sheet                   | reel  | reel            |

| Conductive<br>particles (ACP)    | 1  | 2  | 3  | 4  | 5  |

|----------------------------------|----|----|----|----|----|

| Part. diameter<br>[μm]           | 4  | 5  | 10 | 20 | 30 |

| Conductive<br>material (coating) | Ag | Au | Ag | Ag | Ag |

**Table 1**. (left) Table of commercially available ACF with highlighted number 1 and 2 due to their most common useage. (right) Table of conductive particles available for inhouse ACP mixing.

## 3.2 Flip-chip bonding

ACF is applied to one side of the parts to be connected in a lamination process defined by the manufacturer, while ACP is dispensed by a syringe dispensing system. The dispensing force and the speed of the syringe tip while dispensing is set to control the adhesive quantity. Reducing the quantity of adhesive dispensed without creating uncovered pads due to skipping. For the ACF the quantity of adhesive is controlled by the thickness of the film. A too thick film of ACF will lead to an excess of high-viscosity adhesive resulting in areas of unconnected pixels. For most applications, in particular fine pitch ones, thinner films are therefore preferred. Newest developments in the ACF industry show film thicknesses down to  $10~\mu m$  with embedded metal coated polymer particles of  $3~\mu m$  diameter. Larger particles are required when connecting uneven structures as the particle itself can be deformed to less than half its diameter, therefore evening out the topological differences. Smaller particles in the 3-4  $\mu m$  diameter range however are still in favor for most of fine pitch applications, as reliable connections require a high particle density that can not be realised efficiently with larger particles. For the commercially available ACF like ACF3 or ACF5, simulations of the particle distribution show pads of devices with fine pitch not having a high enough particle yield. An example of a simulation of an ACP particle distribution for a larger

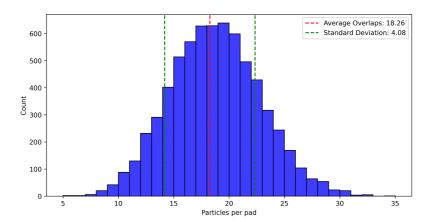

pitch device is shown in Figure 4. The particle placement is picked randomly and then in case of overlap pushed away radially. This is done to emulate the conditions of particles that overlap in 2D top-down view but not 3D view to behave as if thermo-compressed.

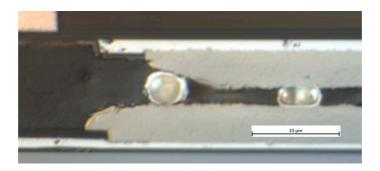

A cross-section analysis shows particles being pinned between nonparallel pad surfaces at an angle of 20° (see Figure 5). This allows for particles being pinned beyond the nominal pad size as the ENIG plating creates round edges around the pad.

**Figure 4.** Histogram of a simulation result showing the distribution of particles pinned per pad. The pads are  $50 \mu m$  in radius while the particles are  $10 \mu m$  in diameter. In this realisation a particle volume fraction of 0.10 is assumed. The total pad count is 6724.

**Figure 5**. Microscopy cross-section picture of an ACP bonded ALTIROC2 ASIC (top) and an LGAD sensor (bottom). Two conductive particles are pinned between the ENIG plated pads, therefore electrically connecting the two pads. The right particle is pinned between two parallel planes while the left on is pinned between two planes at an angle of about 20°.

For the flip-chip process, a device bonder that can apply up to 100 kilograms of force and temperatures up to 400°C is used. The temperature used is dependent on the curing temperature of the epoxy used as adhesive for the ACA. For ACF1 and ACF2 150°C is used as curing temperature while bonding. The bonding pressure used can be as high as 90 MPa for the pad connection area with some devices requiring a lower pressure on the sensor material. For ACP the temperature and bonding pressure applied is generally lower and highly dependent on the materials used. The bonding force is applied till after the cooling of the sample back to room temperature.

## 4 Results

# 4.1 ENIG plating

Consistent plating results for large pitch (>1000 $\mu$ m) substrates with large pads(>50  $\mu$ m in diameter)have been achieved, showing uniform plating heights as desired for the applications. Plating heights for those substrates up to 20  $\mu$ m have been achieved. Other types of substrates show defects limiting the plating to certain ranges depending on the specific layout. Small pitch (<50 $\mu$ m) pixel matrices tend to plate out once growing pads decrease the gap between the pads. For small pads(<20 $\mu$ m diameter) the plating is perturbed and therefore strongly influenced by bath parameters such as temperature, agitation, and concentration of bath constituents. This results in large-pad substrates with small pixel pitches showing plating resilient to perturbations, but early onset of plate out. The plating height for such substrates is therefore limited by the distance between the pixel pad edges. Substrates with large pitches and small pads are dominated by perturbations. Substrates with small pitches and small pads pose the biggest challenge for the current ENIG plating process. ENIG plating on chips with a pixel pitch of 50  $\mu$ m and 7  $\mu$ m pad radius has been achieved up to a plating height of 8  $\mu$ m by carefully controlling stabiliser concentrations and stirring speeds while processing.

### 4.2 Test-Structure Bonding

**Figure 6**. Schematic of a daisy chain device for testing of ACA bonded interconnections.

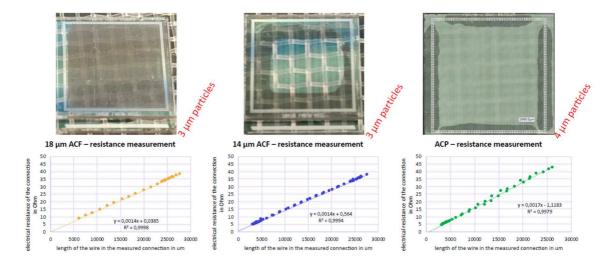

For a systematic characterisation an optimisation of the plating and interconnect process, test devices with a daisy chain connection (see Figure 6) have been designed and produced at FBK (Trento, Italy). These devices have a pixel-pad layout similar to common hybridisation and module interconnect use cases. Three daisy chain structures were produced and bonded that are shown in Figure 7. They emulate an ASIC with a peripheral pad layout on a 20 mm by 20 mm glass substrate. In total 536 connection pads measuring 88  $\mu$ m by 88  $\mu$ m with a 140  $\mu$ m pixel pitch. The ACA used for these tests were ACF1 and ACF2 and one ACP1 with 4  $\mu$ m diameter silver coated conductive particles embedded in Araldite2011. All pads that are covered by the adhesive and have intact read out lines for measuring the resistance show a connection. The electrical resistance is most strongly impacted by the wire length to the readout/measurement pads near the bottom of the device. In the graph the resistances are shown as a function of wire length for the readout connection. The value of electrical resistance per connection chain is calculated to be below 5 Ohms, after deducting the line resistivity. The ACP sample shows a larger statistical spread than the ACF samples, due to the lower particle density of 5% volume fraction used.

**Figure 7**. Pictures of the three different daisy chain devices and their corresponding electrical resistance measurements. On the left is the ACF1 applied as sheet while the ACF used in the device in the middle is made with ACF2 applied in four separate stripes. For the assembly shown on the right the ACP was dispensed in four lines to get a good coverage without risking air entrapment.

## 4.3 LGAD Hybridisation

Developing and testing interconnection of large pitch modules has been done as an alternative for solder bump bonding where additional mechanical strength is required. The ALTIROC2 ASIC[7] as well as the Low Gain Avalanche Detector (**LGAD**)[8] sensors produced by USTC (Hefei, China), have a pixel matrix of 15x15 pixels. The pixel pitch is 1.3 mm and the connecting area per pad is around 8000  $\mu$ m<sup>2</sup>. The adhesive used for bonding is ACP3 with Ag coated 10  $\mu$ m diameter particles. Mechanical samples for cross section microscopy and functional samples have been produced this way. The results of the cross-sections are shown in Figure 8 and Figure 9. The distances between pads in the cross-section measurements are close enough to pin particles in all observed measurements. The functional assembly shows a connection yield of above 98%.

**Figure 8**. Microscopy picture of the cross-section for an ALTIROC2/LGAD device. The connection shown is from row 10 and pad number 7. It shows clearly two particles of 10  $\mu$ m diameter being strongly squished between two ENIG coated pads.

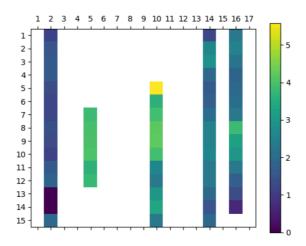

**Figure 9**. 2D map of the cross-section measurements done on the ALTIROC2/LGAD sample. The color coded bar on the right shows the distance in  $\mu$ m between the ENIG pads of the ASIC and sensor. Connections are confirmed for all analysed pads. Row 1 and 17 correspond to pads on the ASIC that connect to the guard ring on the sensor.

## 4.4 SPHIRD Hybridisation

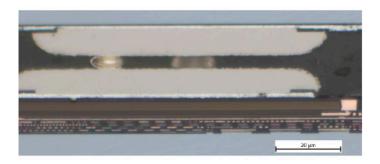

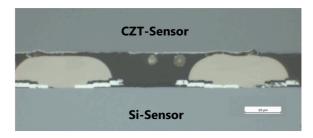

Pixel detector developments for the SPHIRD[9] project of X-ray detectors at the European Synchrotron Radiation Facility (ESRF)(Grenoble, France) use high-Z sensor materials. The hybridization of sensors made of such materials like CZT has proven to be challenging due to the required single-chip processing as well as temperature and pressure sensitivity of the sensors. The ASIC and sensors used in this study contain a pixel matrix of 32x64 pixels with a pitch of  $50 \,\mu m$ . The ASIC is silicon based while various sensor materials (Si, CdTe, CZT)) are used. First preliminary beam test results for an ACF bonded ASIC to silicon sensor made with ACF2 have been achieved. The results of the test-beam study show that 85% of the pixels show a response expected for a good connection while about 7% show a weak response. 7% show no response. Mechanical sample testing has been performed and analysed via microscopy. The mechanical sample tests use an ENIG plated silicon sensor (as ASIC substitution) and an unplated CZT sensor to test bonding on a sample with plating only on the ASIC side. The cross-section pictures in Figure 10 show connections between the pads either via particles or direct pad-to-pad connections.

**Figure 10**. Microscope picture of a cross-section performed on a mechanical assembly of a silicon and a CZT SPHIRD sensor, where only the silicon sensor has been ENIG plated. Particles can bee seen in the small gap between CZT-sensor and ENIG pad.

## 4.5 Timepix3 Hybridisation

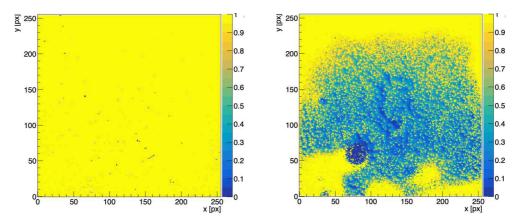

Bonding of Timepix3[10] ASICs to planar silicon sensors of 300  $\mu$ m thickness is performed with ACF. The Timepix3 ASIC has a pixel matrix of 256x256 with one additional row of guard ring pads. The pixel pitch is 55  $\mu$ m and the pad diameter is 12  $\mu$ m. For devices like the Timepix3 the distance from the center of the pixel matrix to the edge of the chip is too large too efficiently squeeze the epoxy out of the matrix. Achieving a sufficient plating height needed to displace the excessive adhesive in gaps between the ENIG pads is challenging. ASIC-side plating of 7-8  $\mu$ m height above the passivation has been achieved with no defects. The bonding has been done with ACF1 and an extended pre bonding step. For this the temperature was kept at 80°C for 600 seconds while the maximum bonding force of 100 kgf was applied, to give the adhesive time to squeeze out of the connection. This was done at reduced temperatures to ensure that the epoxy does not cure prematurely. Afterwards the temperature is raised to 150°C for 5s bonding and full curing.

**Figure 11**. Pixel efficiency maps of a Timepix3 assembly. Obtained from a test-beam measurement with minimum ionizing particles and a reference beam telescope. The left map shows the efficiency close to baseline while the right map shows the efficiency about  $4000 e^-$  from baseline.

The produced device was analysed in a test beam measurement. Figure 11 shows that moderate increase in detection threshold leads to reduced efficiency in the centre regions of the device, as expected from weakly coupled connections. This is assumed to be caused by too large quantities of adhesive in the centre, which could not be squeezed out of the matrix.

## 5 Conclusions

Electrical measurements on dedicated chain devices confirmed that a low-ohmic connection with high interconnect yield can be achieved for large pitch and large pad areas for both ACF and ACP. The results presented for various ASICs and sensors, show promising ACA applications in a wide range of use cases. For large pitch hybridisation it offers an alternative to bump bonding with enhanced mechanical stability provided by the adhesives good interconnect yield. The processes under development have proven beneficial for the R&D efforts of the participating detector projects, due to the fast turnaround and low cost. The results of the SPHIRD project show a not yet sufficient yield for such small-scale and fine pitch devices. ACA shows benefits in the bonding of the

CZT sensors, where standard solder bump bonding is not use able. Simulation results of particle distributions show that a higher particle density is required for a sufficient connection yield. For larger matrices such as Timepix3 the effects relating to adhesive quantity and maximum bonding force of the equipment are to be considered. Currently plating heights sufficient and uniform required to displace the amount of adhesive of the ACFs in use are achieved.

#### 6 Outlook

A higher ENIG plating and/or thinner ACF or a reduced ACF coverage is needed to a achieve a better connection yield for fine pitch assemblies. More daisy chain test structures are being produced for further bonding tests as well as thermal and mechanical testing in a dedicated reliability study. Tests with larger particles for ACP are planned for large pitch applications.

## Acknowledgments

This project has received funding from the European Union's Horizon 2020 Research and Innovation programme under GA no 101004761.

#### References

- [1] MJ Yim and KW Paik, Design and understanding of anisotropic conductive films (ACF's) for LCD packaging, IEEE Transactions on Components, Packaging, and Manufacturing Technology: Part A, 1998, 21, 2, 226-234.

- [2] SM Chang et al., Characteristic study of anisotropic-conductive film for chip-on-film packaging, Microelectronics Reliability, 2011, **41**, 12, 2001-2009.

- [3] P. Svihra et al., Development of novel single-die hybridisation processes for small-pitch pixel detectors, JINST, 2023, 18, C03008.

- [4] J.V. Schmidt et al., *Pixel detector hybridisation with Anisotropic Conductive Films*, *JINST*, 2023, **18**, C01040.

- [5] C. M. Chan et al., Development of novel immersion gold for electroless nickel immersion gold process (ENIG) in PCB applications, 2010 5th International Microsystems Packaging Assembly and Circuits Technology Conference, 2010, 1-4.

- [6] X. Yin et al., Role of a Pb2+ Stabilizer in the Electroless Nickel Plating System: A Theoretical Exploration, J. Phys. Chem. B, 2004, 108, 10919-10929

- [7] ATLAS-HGTD collaboration, M. Morenas, *Performance of ALTIROC2 readout ASIC with LGADs for ATLAS HGTD picosecond MIP timing detector JINST*, 2023, **18**, C01070.

- [8] C.H. Li et al., Performance of LGAD sensors with carbon enriched gain layer produced by USTC, Nuclear Instruments and Methods in Physics Research section A, 2022, **1039**, 167008.

- [9] P. Grybos et al., SPHIRD–Single Photon Counting Pixel Readout ASIC With Pulse Pile-Up Compensation Methods, IEEE Transactions on Circuits and Systems II: Express Briefs, 2023, 70, 3248-3252.

- [10] T. Poikela et al., *Timepix3: a 65K channel hybrid pixel readout chip with simultaneous ToA/ToT and sparse readout JINST* 2014 **9**, C05013.