#### **PAPER • OPEN ACCESS**

## Development of CoRDIA: an Imaging Detector for next-generation Synchrotron Rings and Free Electron Lasers

To cite this article: A Marras et al 2022 J. Phys.: Conf. Ser. 2380 012093

View the article online for updates and enhancements.

### You may also like

- Development of High Performance Electrode of Lithium Ion Battery By High Speed Manufacturing Using Continuous Kneading Process Yukiko Fujita, Kazunori Fukumoto, Yuki Miura et al.

- Continuous group invariances of linear Jahn-Teller systems in icosahedral symmetry: extension to direct sum electronic spaces Robin D Wiseman

- Several generalizations of J. Continuous Functions in Ideal Topological Spaces

P. L. Powar, Vishnu Narayan Mishra and Shikha Bhadauria

**2380** (2022) 012093

doi:10.1088/1742-6596/2380/1/012093

# **Development of CoRDIA: an Imaging Detector for nextgeneration Synchrotron Rings and Free Electron Lasers**

A Marras<sup>1</sup>, A Klujev<sup>1</sup>, S Lange<sup>1</sup>, T Laurus<sup>1</sup>, D Pennicard<sup>1</sup>, U Trunk<sup>1</sup>, C B Wunderer<sup>1</sup>, M L Hafiane<sup>2</sup>, T Hemperek<sup>2</sup>, T Kamilaris<sup>2</sup>, H Krueger<sup>2</sup>, T Wang<sup>2</sup> and H Graafsma<sup>1,3</sup>

- 1) Center for Free-Electron Laser Science CFEL, Deutsches Elektronen-Synchrotron DESY, Germany

- 2) University of Bonn, Bonn, Germany

- 3) Mid Sweden University, Sundsvall, Sweden

corresponding author: alessandro.marras@desy.de

**Abstract.** An x-ray imager is being developed for use in diffraction-limited synchrotron rings and continuous wave free electron lasers. The imager is named CoRDIA (COntinuous Readout Digitising Imager Array) and aims at achieving continuous operation at a frame rate in excess of  $100 \mathrm{kHz}$ . Other goals include single-photon sensitivity at  $12~\mathrm{keV}$  (or below), a full well in excess of  $10 \mathrm{kmphoton/pixel/image}$ , and a  $100 \mathrm{\mu mpixel}$  pitch. The detector ASIC will be compatible with multiple sensor materials to cover different energy ranges. Exploratory prototypes of the readout ASIC (basic circuital blocks) have been manufactured in TSMC 65nm technology: they are presently under test.

#### 1 Introduction

Most of imaging detectors available for photon science experiments today can be roughly divided between the ones capable of continuous operation at moderate speed, i.e. capable of readout at rate up to a few k-frame/s [1,2], often used at synchrotron rings (SRs) and low-repetition-rate free electron lasers (FELs), and the ones optimized for high-repetition-rate FELs, capable of a few M-frame/s, but only for short imaging bursts [3,4,5].

Both the upgrading of SRs to diffraction-limited operation (expected to increase brilliance by two orders of magnitude), and the shift of fast FEL sources from pulsed to continuous wave (CW) operation (which will marginally reduce the peak readout rate requirement, but would make continuous readout a must), points out the common need for bridging the gap between the two categories of detectors, and to provide imaging detectors able to operate continuously at a frame rate in excess of 100k frame/s.

#### 2 CoRDIA development

A collaboration between DESY and Bonn University is developing an instrument to fill this need: the CoRDIA detector (COntinuous Readout Digitising Imager Array).

Content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

**2380** (2022) 012093

doi:10.1088/1742-6596/2380/1/012093

Our goals include continuous operation between 100 and 200 kframe/s, single-photon sensitivity at 12 keV (or below), a full well in excess of 10k photon/pixel/image, and a 100µm pixel pitch.

The detector system will be built up as a multi-module array of hybrid assembles, including a common readout ASIC compatible with multiple sensor materials: p-doped Silicon for the main (10 keV) energy range, high-Z materials for higher energies, and sensors with built-in amplification for soft X-rays (below 3keV).

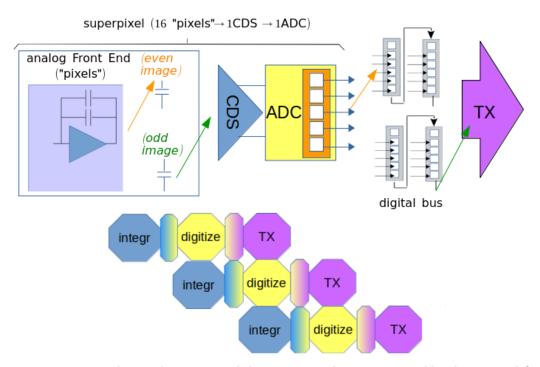

The ASIC uses a continuous writing-reading (CWR) approach based on a pipelined signal processing chain, so that while one image is being integrated, the previous image is digitized by onchip ADCs, and the image before that is streamed out through a fast driver.

For the analog front end, we have designed an adaptive-gain charge-integrating block inspired by the AGIPD detector [6], able to adjust the system gain to the incoming photon flux.

Similarly, a correlated-double-sampling (CDS) circuit hs been designed to reduce noise.

We have designed an ADC using a successive approximation architecture with reduced size, so that it can be integrated in a modular "superpixel" structure within the pixel array. Digitization speed has been defined so that multiple (16) analog front ends can feed feeding sequentially a circuit for a CDS and being digitized by an ADC without hampering the frame rate.

For the digital readout, we plan to adopt the principle of the gigabit wire transmitter (GWT) solution developed by NIKHEF for Timepix4 [7]. While we have not yet redesigned this block yet, we reached an agreement for the the reuse of the NIKHEF-developed layout.

An overview of proposed the pipeline achitecture is presented in Figure 1.

**Figure 1.** CoRDIA pipeline architecture. While an image is being integrated by the preamplifier into a capacitor, the former image is retrieved by a second capacitor and passed to the Correlated-Double-Sampling (CDS) and ADC circuit. Similarly, while an image is being digitized, the image before is sent out through the transmitter (TX) block. The signal path alternates for even (orange) and odd (green) images in a "ping-pong" fashion, allowing continuous Continuous Writing-Reading (CWR)

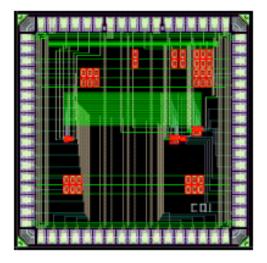

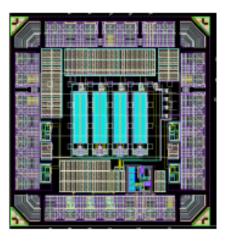

Exploratory prototypes (Figure 2) of the readout ASIC basic circuit blocks have been designed in TSMC 65nm technology and have been manufactured in an Multi Project Wafer (MPW), also using IPs provided b CERN and by the RD53 collaboration.

**2380** (2022) 012093

doi:10.1088/1742-6596/2380/1/012093

Circuit solutions have been included in the MPW to validate the charge-integrating block and the Correlated Double Sampling stage, both as isolated blocks and as pipelined stages. Four ADC variants have been included, to explore redundancy and advanced-switching options in the digitization process. The circuits are presently under test.

Our present goal is to test indvidual components to verify that each stage of our pipleline is not a critical bottleneck for our frame rate aims: preliminary tests suggest that a continuous frame rate in excess of 150kHz would be achieveable. Details of the test results will follow in future publications.

**Figure 2.** CoRDIA basic circuit block prototypes. Left: front-end analog circuits. Right: ADC variants

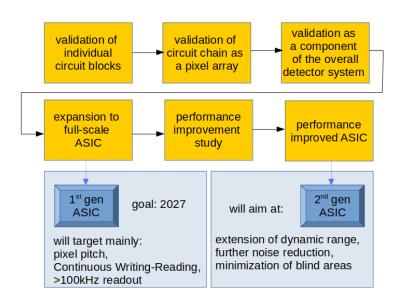

After test and validation of single circuit blocks, we plan to follow a gradual approach (Figure 3), first developing a 1st-generation ASIC that, while usable for scientific experiments, will achieve only some of our goals (targeting mainly pixel pitch, continuous writing-reading operation and frame rate). Our aim is to have this first version available by DESY's PETRA IV start of operation, about 2027.

The 1st-generation ASIC will be followed by a 2nd-generation ASIC, that will correct eventual bugs and aim at extending dynamic range, reducing noise, and minimizing blind areas.

**Figure 3.** CoRDIA overall project plan.

**2380** (2022) 012093

doi:10.1088/1742-6596/2380/1/012093

Even for an array of just 1Mpixel and for a reduced frame rate at the bottom of our range (100k frame/s), the detector is foreseen to produce a signficative data output, of the order of 1.4 Tb/s. For our goal frame rate of 150k frame/s, and considering some overhead coming from data padding and encoding, the throughput might easily get over 2Tb/s.

We plan to address the issue both on-Silicon (by means of on-chip digitization through parallel ADCs, as a digital streamout allows the use of high speed drivers, like the chosen GWT), and out-of-Silicon (by using high-performance FPGAs to serialize the data, and high-speed optical links). Hardware acceleration solutions for image correction and conventional compression methods are under consideration, as well as data reduction schemes on preprocessing hardware, to reduce the data volume arriving to later processing stages.

#### **3 Conclusions**

An X-Ray Imager is being developed, for diffraction-limited synchrotron rings and continuous wave free electron lasers.

Its main feature is being capable of continuous image acquisition at high frame rate (>100kHz). The general architecture has been defined, and basic circuital blocks have been designed and manufactured in an MPW they are presently under test.

We aim for the first generation of the detector to be usable by the start of operation of the diffraction-limited upgrade of DESY storage ring (Petra IV), about 2027.

#### References

- 1 D Pennicard et al, "The LAMBDA photon-counting pixel detector and high-Z sensor development" 2014 JINST 9 C12026

- 2 A Mozzanica et al., "Characterization results of the JUNGFRAU full scale readout ASIC", Journal of Instrumentation. 2016; 11(2): C02047 (8 pp.)

- 3 A. Allahgholi et al., "AGIPD, a high dynamic range fast detector for the European XFEL", 2015 JINST 10 C01023

- 4 M. Donato et al., "First functionality tests of a  $64 \times 64$  pixel DSSC sensor module connected to the complete ladder readout", 2017 JINST 12 C03025

- 5 M.C. Veale et al., "Characterisation of the high dynamic range Large Pixel Detector (LPD) and its use at X-ray free electron laser sources", 2017 JINST 12 P12003

- 6 D Greiffenberg, "The AGIPD detector for the European XFEL", 2012 JINST 7 C01103

- 7 X. Llopart et al., "Timepix4, a large area pixel detector readout chip which can be tiled on 4 sides providing sub-200 ps timestamp binning", 2022 JINST 17 C01044