# The ABC130 barrel module prototyping programme for the ATLAS strip tracker

To cite this article: L. Poley et al 2020 JINST 15 P09004

View the <u>article online</u> for updates and enhancements.

## IOP ebooks™

Bringing together innovative digital publishing with leading authors from the global scientific community.

Start exploring the collection-download the first chapter of every title for free.

RECEIVED: June 5, 2020 ACCEPTED: June 20, 2020 Published: September 3, 2020

## The ABC130 barrel module prototyping programme for the **ATLAS** strip tracker

- L. Poley, 1,\* C. Sawyer, 2 S. Addepalli, 3 A.A. Affolder, 4 B. Allongue, 5 P. Allport, 6 E. Anderssen, F. Anghinolfi, J.-F. Arguin, J.-H. Arling, O. Arnaez, N.A. Asbah, 10

- J. Ashby, 11 E.M. Asimakopoulou, 12 N.B. Atlay, 13 L. Bartsch, 4 M.J. Basso, 9 J. Beacham, 14

- S.L. Beaupré, <sup>15</sup> G. Beck, <sup>16</sup> C. Beichert, <sup>13</sup> L. Bergsten, <sup>3</sup> J. Bernabeu, <sup>17</sup> P. Bhattarai, <sup>3</sup>

- I. Bloch,<sup>8</sup> A.J. Blue,<sup>11</sup> M. Bochenek,<sup>18</sup> J. Botte,<sup>19</sup> L. Boynton,<sup>20</sup> R. Brenner,<sup>12</sup> B. Brueers,<sup>8</sup>

- E. Buchanan, 21,22 B. Bullard, 10 F. Capocasa, 3 I. Carr, 23 S. Carra, 8 C.W. Chao, 7 J. Chen, 3

- L. Chen, 21,22,24 Y. Chen, 21,22,24 X. Chen, 25 V. Cindro, 26 A. Ciocio, 1 J. V. Civera, 17 K. Cormier, 9

- E. Cornell, B. Crick, W. Dabrowski, M. Dam, C. David, G. Demontigny, K. Dette,

- J. DeWitt, S. Diez, F. Doherty, J. Dopke, N. Dressnandt, S. Edwards, V. Fadeyev,

- S. Farrington,<sup>31</sup> W. Fawcett,<sup>32</sup> J. Fernandez-Tejero,<sup>33</sup> E. Filmer,<sup>34</sup> C. Fleta,<sup>33</sup> B. Gallop,<sup>2</sup>

- Z. Galloway, 4 C. Garcia Argos, 35 D. Garg, 36 M. Gignac, 4 D. Gillberg, 19 D. Giovinazzo, 4

- J. Glover, P. Goettlicher, L. Gonella, A. Gorišek, C. Grant, F. Grant, C. Gray, 11

- A. Greenall, <sup>20</sup> I. Gregor, <sup>8</sup> G. Greig, <sup>15</sup> A. A. Grillo, <sup>4</sup> S. Gu, <sup>37</sup> F. Guescini, <sup>38</sup>

- J. Barreiro Guimaraes da Costa, 21,22 J. Gunnell, R. Gupta, C. Haber, A. Halgheri, 18

- D. Hamersly,<sup>4</sup> T.E. Haugen,<sup>1</sup> M. Hauser,<sup>35</sup> S. Heim,<sup>8</sup> T. Heim,<sup>1</sup> C. Helling,<sup>4</sup> H. Herde,<sup>3</sup>

- N. P. Hessey,<sup>38</sup> B. Hommels,<sup>32</sup> J.C. Hönig,<sup>35</sup> A. Hunter,<sup>6</sup> P. Jackson,<sup>34</sup> K. Jewkes,<sup>31</sup>

- J.J. John, <sup>39</sup> T.A. Johnson, <sup>1</sup> T. Jones, <sup>20</sup> S. Kachiguin, <sup>4</sup> N. Kang, <sup>4</sup> J. Kaplon, <sup>5</sup> M. Kareem, <sup>29</sup>

- P. Keener, <sup>18</sup> J. Keller, <sup>19</sup> M. Key-Charriere, <sup>2</sup> S. Kilani, <sup>40</sup> D. Kisliuk, <sup>9</sup> C.T. Klein, <sup>32</sup> T. Koffas, <sup>19</sup>

- G. Kramberger, <sup>26</sup> K. Krizka, <sup>1</sup> J. Kroll, <sup>41</sup> S. Kuehn, <sup>35</sup> M. Kurth, <sup>21,22,24</sup> C. Labitan, <sup>1</sup> C. Lacasta, <sup>17</sup>

- H. Lacker, <sup>13</sup> P. León, <sup>17</sup> B. Li, <sup>1,25</sup> C. Li, <sup>1</sup> Y. Li, <sup>21,22</sup> Z. Li, <sup>39</sup> Z. Liang, <sup>21,22</sup> M. Liberatore, <sup>8</sup>

- A. Lister,<sup>42</sup> K. Liu,<sup>21,22</sup> P. Liu,<sup>21,22</sup> T. Lohse,<sup>13</sup> J. Lönker,<sup>43</sup> X. Lou,<sup>21,22,24</sup> W. Lu,<sup>21,22</sup> Z. Luce,<sup>4</sup>

- D. Lynn, 44 R. MacFadyen, 1 S. Mägdefessel, 35 K. Mahboubi, 35 U. Malik, 36 I. Mandić, 26

- D. La Marra, <sup>45</sup> J. Martin, <sup>7</sup> F. Martinez-Mckinney, <sup>4</sup> M. Mikestikova, <sup>41</sup> M. Mikuž, <sup>26</sup> A. Mitra, <sup>31</sup>

- E. Mladina, A. Montalbano, D. Monzat, M. Morii, G. Mullier, 46 J. Neundorf, 8

- M. Newcomer, 18 Y. Ng, 13 A. Nikolica, 18 K. Nikolopoulos, 6 J. Oechsle, 28 J. Oliver, 34 R.S. Orr, 9

- G. Ottino,<sup>1</sup> C. Paillard,<sup>5</sup> P. Pani,<sup>8</sup> S. Paowell,<sup>20</sup> U. Parzefall,<sup>35</sup> P. W. Phillips,<sup>2</sup> A. Platero,<sup>17</sup>

- V. Platero, <sup>17</sup> V. Prahl, <sup>8</sup> S. Pyatt, <sup>6</sup> K. Ran, <sup>21,22,24</sup> N. Reardon, <sup>23</sup> L. Rehnisch, <sup>13</sup> A. Renardi, <sup>8</sup>

- M. Renzmann, O. Rifki, A. Rodriguez Rodriguez, G. Rosin, E. Rossi, T. Ruggeri, 4

- F. Rühr,<sup>35</sup> P. Rymaszewski,<sup>5</sup> H.F.-W. Sadrozinski,<sup>4</sup> P. Sanethavong,<sup>1</sup> S. Neha Santpur,<sup>1</sup>

- C. Scharf, 13 Z. Schillaci, 3 S. Schmitt, 8 A. Sharma, 34 G. Sciolla, 3 A. Seiden, 4 X. Shi, 21,22

<sup>\*</sup>Corresponding author.

- C. Simpson-Allsop,<sup>6</sup> H. Snoek,<sup>48</sup> S. Snow,<sup>31</sup> C. Solaz,<sup>17</sup> U. Soldevila,<sup>17</sup> F. Sousa,<sup>5</sup>

- D. Sperlich, 35 E. Staats, 19 T.L. Stack, 38 M. Stanitzki, 8 N. Starinsky, 7 J. Steentoft, 12

- M. Stegler,<sup>8</sup> B. Stelzer,<sup>15</sup> S. Stucci,<sup>44</sup> K. Swientek,<sup>27</sup> G.N. Taylor,<sup>23</sup> W. Taylor,<sup>29</sup> J. Jian Teoh,<sup>48</sup>

- R. Teuscher, J. Thomas, A. Tigchelaar, T. Tran, A. Tricoli, 4 D.A. Trischuk, 2 Y. Unno, 49

- G. van Nieuwenhuizen, 44 M. Ullán, 33 J. Vermeulen, 48 P. Vicente Leitao, 5 T. Vickey, 30

- G. Vidal, <sup>17</sup> M. Vreeswijk, <sup>48</sup> M. Warren, <sup>40</sup> T. Weidberg, <sup>39</sup> M. Wiehe, <sup>35</sup> C. Wiglesworth, <sup>28</sup>

- L. Wiik-Fuchs, 35 S. Williams, 23 J. Wilson, 6 R. Witharm, 1 F. Wizemann, 43 S. Wonsak, 20

- S. Worm, <sup>6,8</sup> M. Wormald, <sup>20</sup> S. Xella, <sup>28</sup> Y. Yang, <sup>21,22</sup> J. Yarwick, <sup>4</sup> T. Yu, <sup>31</sup> D. Zhang, <sup>25</sup>

- K. Zhang,  $^{21,22,24}$  M. Zhou $^{21,22,24}$  and H. Zhu $^{21,22}$

<sup>&</sup>lt;sup>1</sup>Lawrence Berkeley National Laboratory, Cyclotron Road, Berkeley, U.S.A.

<sup>&</sup>lt;sup>2</sup>Particle Physics Department, STFC Rutherford Appleton Laboratory, Harwell Science and Innovation Campus, Didcot, United Kingdom

<sup>&</sup>lt;sup>3</sup>Martin A. Fisher School of Physics, Brandeis University, Waltham, United States of America

<sup>&</sup>lt;sup>4</sup>Santa Cruz Institute of Particle Physics, University of California, High Street, Santa Cruz, United States of America

<sup>&</sup>lt;sup>5</sup>Experimental Physics Department, CERN, Geneva, Switzerland

<sup>&</sup>lt;sup>6</sup>School of Physics and Astronomy, University of Birmingham, Edgabston, Birmingham, United Kingdom

<sup>&</sup>lt;sup>7</sup>Group of Particle Physics, University of Montreal, Rue University, Montreal, Canada

<sup>&</sup>lt;sup>8</sup>Deutsches Elektronen-Synchrotron, Notkestraße, Hamburg, Germany

<sup>&</sup>lt;sup>9</sup>Department of Physics, University of Toronto, Saint George St., Toronto, Canada

<sup>&</sup>lt;sup>10</sup>Jefferson Laboratory of Physics, Harvard University, Oxford Street, Cambridge, United States of America

<sup>&</sup>lt;sup>11</sup>SUPA School of Physics and Astronomy, University of Glasgow, University Avenue, Glasgow, United Kingdom

<sup>&</sup>lt;sup>12</sup>Department of Physics and Astronomy, Uppsala Universitet, Uppsala, Sweden

<sup>&</sup>lt;sup>13</sup>Institut für Physik, Humboldt-Universität zu Berlin, Berlin, Germany

<sup>&</sup>lt;sup>14</sup>Department of Physics, Duke University, Science Dr., Durham, U.S.A.

<sup>&</sup>lt;sup>15</sup>Department of Physics, Simon Fraser University, University Drive W, Burnaby, Canada

<sup>&</sup>lt;sup>16</sup>School of Physics and Astronomy, Queen Mary University of London, Mile End Road, London, United Kingdom

<sup>&</sup>lt;sup>17</sup>Instituto de Física Corpuscular, CSIC-Universidad de Valencia, c/ Catedrático José Beltrán, Paterna, Spain

<sup>&</sup>lt;sup>18</sup>Department of Physics and Astronomy, University of Pennsylvania, South 33rd Street, Philadelphia, U.S.A.

<sup>&</sup>lt;sup>19</sup>Department of Physics, Carleton University, Colonel By Drive, Ottawa, Canada

<sup>&</sup>lt;sup>20</sup>Department of Physics, University of Liverpool, Oxford Street, Liverpool, United Kingdom

<sup>&</sup>lt;sup>21</sup>Institute of High Energy Physics, Yuquan Road, Beijing, China

<sup>&</sup>lt;sup>22</sup>State Key Laboratory of Particle Detection and Electronics, Beijing, China

<sup>&</sup>lt;sup>23</sup>School of Physics, The University of Melbourne, Swanston Street, Parkville, Australia

<sup>&</sup>lt;sup>24</sup>University of Chinese Academy of Sciences, Yuquan Road, Beijing, China

<sup>&</sup>lt;sup>25</sup>Department of Physics, Tsinghua University, Beijing, China

<sup>&</sup>lt;sup>26</sup>Jožef Stefan Institute and Department of Physics, University of Ljubljana, Jadranska ulica, Ljubljana, Slovenia

<sup>&</sup>lt;sup>27</sup> Faculty of Physics and Applied Computer Science, AGH University of Science and Technology, al. Mickiewicza, Krakow, Poland

<sup>&</sup>lt;sup>28</sup>Niels Bohr Institute, University of Copenhagen, Blegdamsvej, Copenhagen, Denmark

E-mail: APoley@cern.ch, craig.sawyer@stfc.ac.uk

ABSTRACT: For the Phase-II Upgrade of the ATLAS Detector [1], its Inner Detector, consisting of silicon pixel, silicon strip and transition radiation sub-detectors, will be replaced with an all new 100 % silicon tracker, composed of a pixel tracker at inner radii and a strip tracker at outer radii. The future ATLAS strip tracker will include 11,000 silicon sensor modules in the central region (barrel) and 7,000 modules in the forward region (end-caps), which are foreseen to be constructed over a period of 3.5 years. The construction of each module consists of a series of assembly and quality control steps, which were engineered to be identical for all production sites. In order to develop the tooling and procedures for assembly and testing of these modules, two series of major prototyping programs were conducted: an early program using readout chips designed using a 250 nm fabrication process (ABCN-250) [2, 3] and a subsequent program using a follow-up chip set made using 130 nm processing (ABC130 and HCC130 chips). This second generation of readout chips was used for an extensive prototyping program that produced around 100 barrel-type modules and contributed significantly to the development of the final module layout. This paper gives an overview of the components used in ABC130 barrel modules, their assembly procedure and findings resulting from their tests.

Keywords: Detector design and construction technologies and materials; Si microstrip and pad detectors; Radiation-hard detectors; Front-end electronics for detector readout

<sup>&</sup>lt;sup>29</sup>Department of Physics and Astronomy, York University, Keele Sreet, Toronto, Canada

<sup>&</sup>lt;sup>30</sup>Department of Physics and Astronomy, University of Sheffield, Hounsfield Road, Sheffield, United Kingdom

<sup>&</sup>lt;sup>31</sup>Department of Physics, University of Warwick, Coventry, United Kingdom

<sup>&</sup>lt;sup>32</sup>Department of Physics, Cavendish Laboratory, J. J. Thomson Avenue, Cambridge, United Kingdom

<sup>&</sup>lt;sup>33</sup>Centro Nacional de Microelectrónica (IMB-CNM), Campus UAB-Bellaterra, Barcelona, Spain

<sup>&</sup>lt;sup>34</sup>Department of Physics, University of Adelaide, Adelaide, Australia

<sup>&</sup>lt;sup>35</sup>Physikalisches Institut, Albert-Ludwigs-Universität Freiburg, Hermann-Herder-Straße, Freiburg im Breisgau, Germany

<sup>&</sup>lt;sup>36</sup>Department of Physics and Astronomy, The University of Iowa, Iowa City, United States of America

<sup>&</sup>lt;sup>37</sup>Beihang University, Xueyuan Road, Beijing, China

<sup>&</sup>lt;sup>38</sup>TRIUMF, Wesbrook Mall, Vancouver, Canada

<sup>&</sup>lt;sup>39</sup>Physics Department, Oxford University, Keble Rd, Oxford, United Kingdom

<sup>&</sup>lt;sup>40</sup>Department of Physics and Astronomy, University College London, Gower Street, London, United Kingdom

<sup>&</sup>lt;sup>41</sup>Institute of Physics of the Czech Academy of Sciences, Na Slovance, Prague, Czech Republic

<sup>&</sup>lt;sup>42</sup>University of British Columbia, Department of Physics, Agricultural Road, Vancouver, Canada

<sup>&</sup>lt;sup>43</sup>Lehrstuhl für Experimentelle Physik IV, Technische Universität Dortmund, Otto-Hahn-Straße, Dortmund, Germany

<sup>&</sup>lt;sup>44</sup>Brookhaven National Laboratory, Rochester Street, Upton, United States of America

<sup>&</sup>lt;sup>45</sup>Département de physique nucléaire et corpusculaire, Université de Genève, quai Ernest-Ansermet, Genève, Switzerland

<sup>&</sup>lt;sup>46</sup>Division of particle physics, Lunds Universitet, Lund, Sweden

<sup>&</sup>lt;sup>47</sup>Department of Physics, University of Massachusetts, North Pleasant Street, Amherst, United States of America

<sup>&</sup>lt;sup>48</sup>Nikhef National Institute for Subatomic Physics, University of Amsterdam, Science Park, Amsterdam, Netherlands

<sup>&</sup>lt;sup>49</sup>Institute of Particle and Nuclear Study, KEK, Oho, Tsukuba, Japan

### Contents

| 1 | Intro                     | oduction                                                | 1             |  |  |

|---|---------------------------|---------------------------------------------------------|---------------|--|--|

| 2 | Components                |                                                         |               |  |  |

|   | 2.1                       |                                                         | <b>1</b><br>2 |  |  |

|   | 2.2                       | Readout chips                                           | 5             |  |  |

|   |                           | 2.2.1 ABC130                                            | 5             |  |  |

|   |                           | 2.2.2 HCC130                                            | 17            |  |  |

|   |                           | 2.2.3 AMACv1a                                           | 18            |  |  |

|   | 2.3                       | Hybrids                                                 | 20            |  |  |

|   | 2.4                       | Powerboard                                              | 22            |  |  |

| 3 | Mod                       | ule construction                                        | 24            |  |  |

|   | 3.1                       | Hybrid assembly                                         | 25            |  |  |

|   | 3.2                       | Electrical tests of hybrids and modules                 | 28            |  |  |

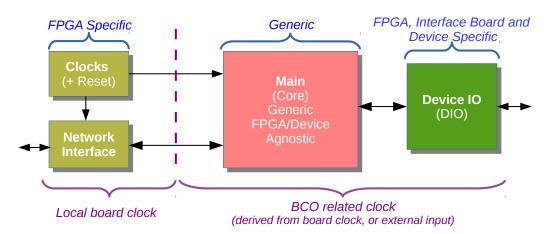

|   |                           | 3.2.1 Physical DAQ system                               | 28            |  |  |

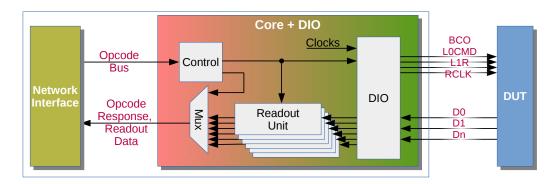

|   |                           | 3.2.2 PC/firmware interface                             | 29            |  |  |

|   |                           | 3.2.3 Firmware structure                                | 30            |  |  |

|   |                           | 3.2.4 Opcode sub-system                                 | 32            |  |  |

|   |                           | 3.2.5 Software                                          | 32            |  |  |

|   |                           | 3.2.6 Characterisation tests                            | 34            |  |  |

|   | 3.3                       | Hybrid tests                                            | 38            |  |  |

|   | 3.4                       | Powerboard assembly                                     | 40            |  |  |

|   | 3.5                       | Powerboard tests                                        | 40            |  |  |

|   | 3.6                       | Sensor tests                                            | 41            |  |  |

|   | 3.7                       | Module assembly                                         | 41            |  |  |

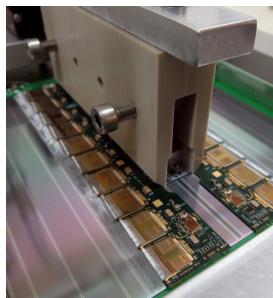

|   |                           | 3.7.1 Sensor metrology after module assembly            | 47            |  |  |

|   | 3.8                       | Module tests                                            | 48            |  |  |

| 4 | Selec                     | cted module test results                                | 50            |  |  |

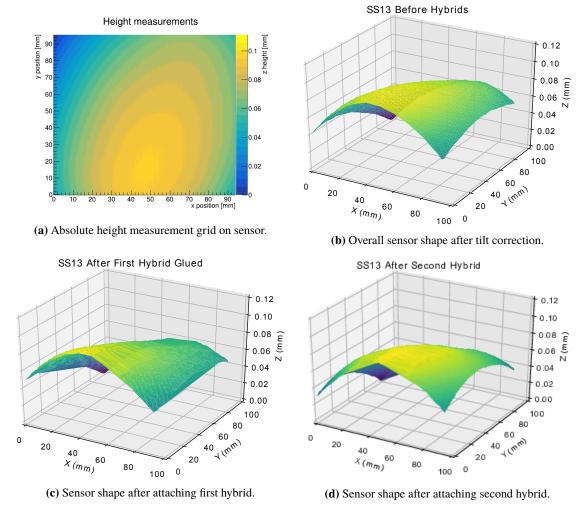

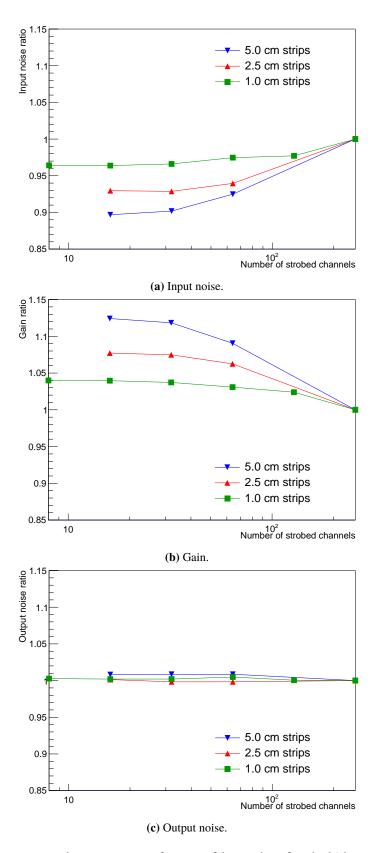

|   | 4.1                       | Dependence on number of strobed channels and triggers   | 50            |  |  |

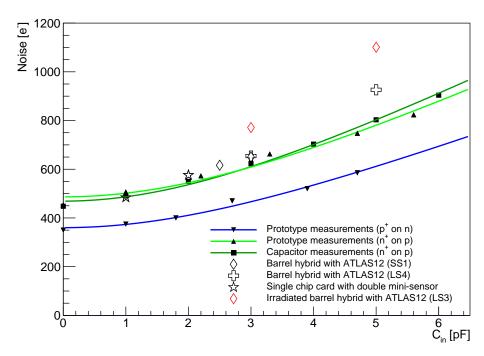

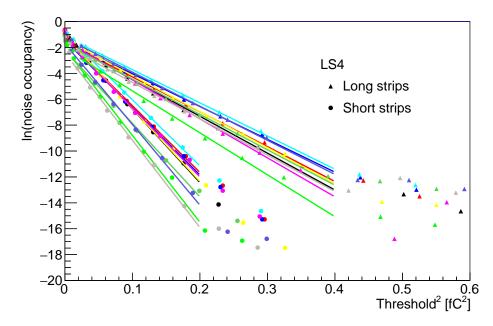

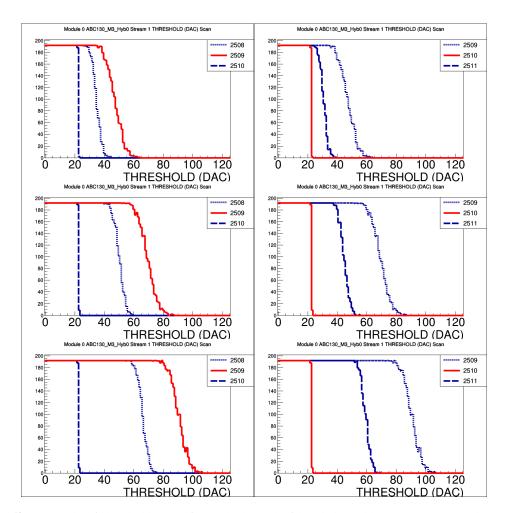

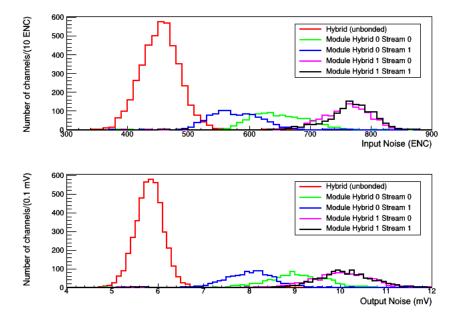

|   | 4.2                       | Module noise and strip capacitance                      | 51            |  |  |

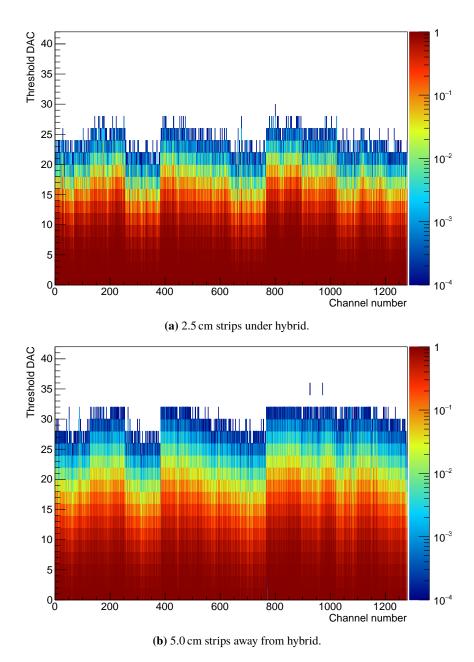

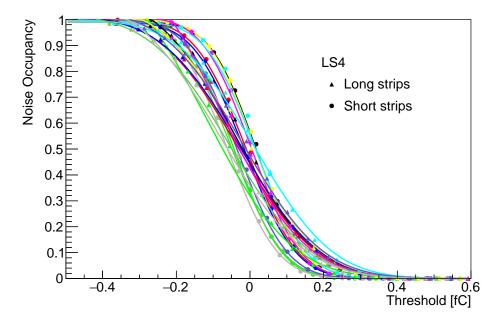

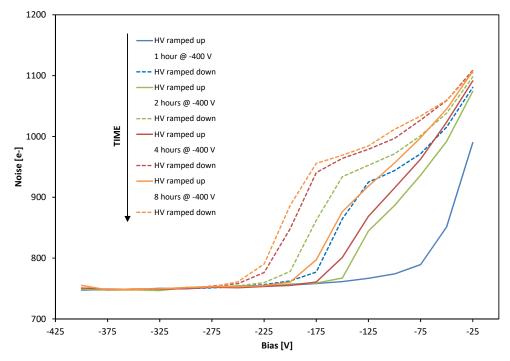

|   | 4.3                       | Noise occupancy results                                 | 54            |  |  |

|   | 4.4                       | Comparison between Noise Occupancy and Three Point Gain | 56            |  |  |

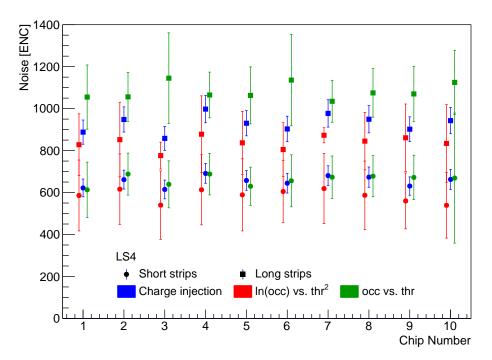

|   | 4.5                       | Sensor hysteresis                                       | 57            |  |  |

|   | 4.6                       | EMI pick up studies                                     | 58            |  |  |

|   | 4.7                       | Effect of powerboard on module noise                    | 61            |  |  |

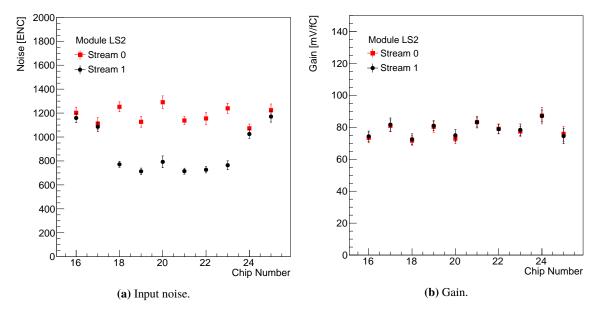

|   | 4.8                       | Irradiated modules                                      | 65            |  |  |

|   | 4.9                       | Bad channel identification                              | 65            |  |  |

|   |                           | 4.9.1 Electrical shorts                                 | 65            |  |  |

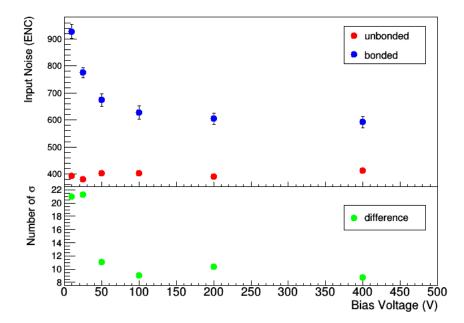

|   |                           | 4.9.2 Unbonded classification and bias voltage          | 68            |  |  |

|   | 4.10                      | Current increase with Total Ionising Dose (TID bump)    | 69            |  |  |

| 5 | Conclusion and outlook 70 |                                                         |               |  |  |

#### 1 Introduction

For the High-Luminosity Upgrade of the Large Hadron Collider, the ATLAS [1] Inner Detector will be replaced with a new, all silicon Inner Tracker (ITk), composed of a pixel tracker [4] and a strip tracker [5].

The main component of the ITk strip tracker is the module, comprising a silicon strip sensor, multiple custom readout chips mounted on a electronic circuit, called a hybrid, and a powerboard. In the central region of the ITk strip detector, the four barrel layers comprise 11,000 modules mounted on staves such that the sensors are arranged parallel to the beam axis (see figure 1a). The two end-caps in the forward region are constructed from six disks supporting a total of 7,000 modules mounted on petals such that the sensors are arranged orthogonal to the beam axis (see figure 1b).

Modules in the strip tracker barrel and end-caps were designed to contain the same materials and components, which have the same functionality, but different geometries. Only two types of sensors are used in the barrel region, whereas six sensor geometries are required for hermetic coverage of the end-cap. Here, only modules designed for the barrel region are presented.

An extensive prototyping program was conducted in preparation for the production of 11,000 barrel modules at ten construction sites in the US, UK and China. The aim of the prototyping programme was to develop realistic tests of the concepts for tooling and assembly, readout software and testing procedures, hence, the prototype modules use readout chips, sensors and other components similar to those foreseen to be used in production.

#### 2 Components

In the central region of the ITk strip tracker (barrel), two versions of modules are used:

- short strip (SS) modules in the inner two barrel layers, where each sensor strip has a length of about 2.5 cm

- long strip (LS) modules in the outer two barrel layers, with sensor strip lengths of about 5 cm

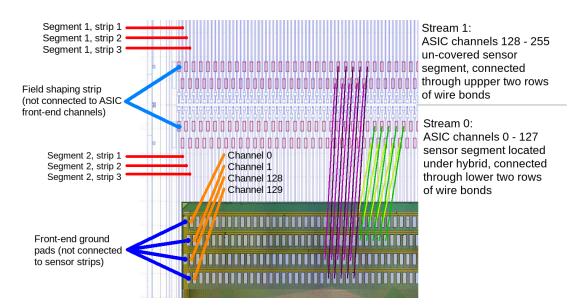

Despite their different strip lengths, both module types have similar sizes, which are determined by the size of the silicon strip sensor (about  $10 \times 10 \,\mathrm{cm^2}$  each). Therefore, strips are arranged in two rows on LS sensors and in four rows on SS sensors (the terms row and segment are used interchangeably throughout this manuscript), where each row consists of 1280 signal strips and two unconnected edge strips (see figures 2a and 2b). Accordingly, LS modules require 2560 readout channels (corresponding to 10 ABC130 readout chips with 256 channels each) and SS modules 5120 (corresponding to 20 ABC130 readout chips).

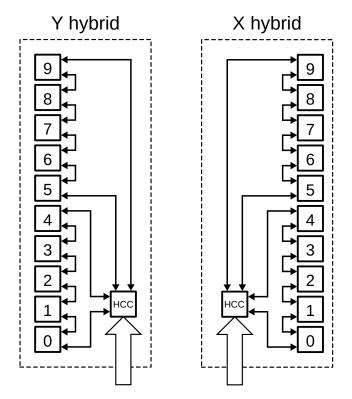

Despite requiring different numbers of readout channels and chips, electronic components for barrel modules were designed to be compatible with both sensor geometries. Flexible circuit boards supporting ABC130 readout chips, called hybrids (section 2.3), were designed, with one hybrid required per two strip segments. An SS module uses two such hybrids, an X-type and a Y-type version, whereas an LS module uses only one X-type hybrid (see figures 3a and 3b). Flex circuit boards called powerboards (section 2.4), which support a DCDC power converter, high voltage switch and a monitoring chip, match both LS and SS module layouts, thereby minimising the number of components to be designed, tested and qualified for production.

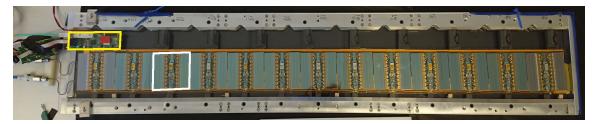

(a) Stave for the ITk strip tracker barrel: thirteen modules are arranged in one row.

(b) Petal for the ITk strip tracker end-caps: six modules are arranged in six rings.

**Figure 1.** Support structures with modules for the ITk strip tracker barrel (composed of staves) and end-caps (consisting of petals). Sensor strips on staves are aligned parallel to the beam axis modulo a 26 mrad stereo angle on either side of the stave whilst strips on petals are arranged perpendicular to the beam axis with a 20 mrad stereo angle implemented into the sensors themselves. An individual module is indicated in white, with sensor strip implants oriented perpendicular to the hybrids on each module segment. The end-of-substructure card (see [5]) of each structure is indicated in yellow. In the outer three rings of the end-cap so-called split modules are implemented due to the limited area of 6 inch silicon wafers so that each ring module contains two silicon strip modules.

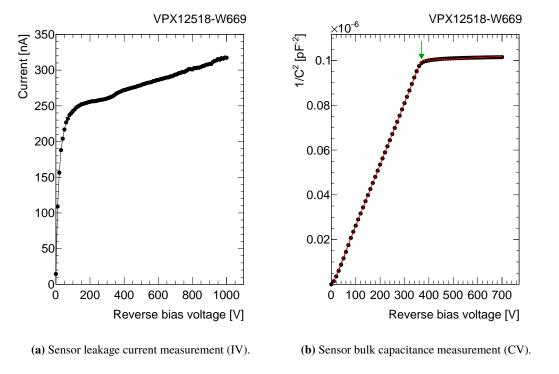

#### 2.1 Sensors

Short strip modules for the ABC130 barrel module program were constructed using ATLAS12 barrel sensors [6], a prototype version of the sensors to be used in the ATLAS ITk developed from the predecessor ATLAS07 sensors [7]. The sensors are fabricated from 6-inch floatzone wafers in a single-sided process.

The sensors have a nominal thickness of  $310 \pm 20\,\mu m$  with a maximum thickness variation of  $10\,\mu m$  across the sensor area. After dicing, ATLAS12 sensors have a size of  $96.7 \times 96.6\,mm^2$ . Compared to ATLAS07 sensors, the dead space in periphery of the sensor was reduced from approximately 1 mm to  $500\,\mu m$  per edge.

(a) ATLAS17LS sensor with two segments containing long strips with a length of about 5 cm each and two rows of bond pads per segment.

**(b)** ATLAS12SS sensor with four short strip segments (strip length about 2.5 cm) and five rows of bond pads per segment.

**Figure 2.** ATLAS barrel long strip and short strip sensors used for the construction of ABC130 barrel modules. Sensor strips are oriented horizontally, with each segment comprising 1282 sensor strips. The vertical lines seen here are rows of the bond pads, the only large-scale feature in the strip area discernible by eye.

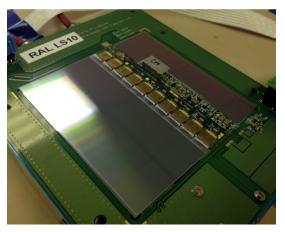

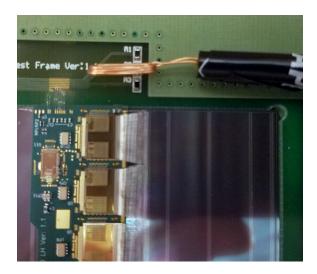

(a) ABC130 LS barrel module on an LS test frame: one X-type hybrid is mounted at the border between LS strip segments with the powerboard mounted on the same segment.

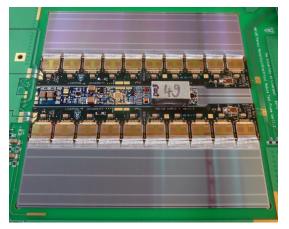

**(b)** ABC130 SS module on an SS test frame: one X-type hybrid and a Y-type are mounted at the borders between two short strip segments with one powerboard between them.

Figure 3. ABC130 long-strip and short-strip modules.

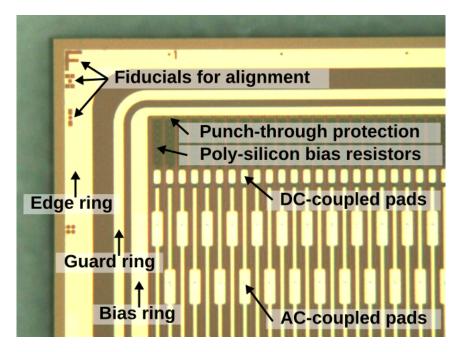

Figure 4. Detail image of an ATLAS barrel sensor and its design features.

Each ATLAS12SS sensor consists of four segments with 1282 strip implants each, where the first and last strip serve as field shaping strips. The strips have a length of 23.9 mm and a strip pitch of  $74.5 \, \mu m$ .

In order to cope with the high-radiation environment of the ITk, strip sensors are made from p-doped bulk material with n<sup>+</sup>-doped strip implants. The bulk remains as p-doped after radiation damage, therefore the sensor depletion zone grows from the strip implant side towards the backside, allowing for a significant signal collection even when operated underdepleted due to radiation damage at the end-of life fluence. Each n<sup>+</sup>-doped strip implant is connected to an n-doped implant ring surrounding all strip implants (bias ring) to hold all strip implants at the same potential during operation. The bias ring is surrounded by another n-doped implant ring (guard ring) and a p-doped implant ring (edge ring) laid-out next to the dicing edge. Figure 4 shows an overview of the different sensor design features. This edge ring prevents the depleted region, evolving from the bias ring, from extending to and along the dicing edge between the edge ring and the p-doped backplane (held at high voltage), and is needed to prevent an early breakdown [8]. Detailed studies of the electrical properties of the ATLAS12 can be found in [9].

With increasing radiation damage, the  $Si/SiO_2$  passivation layer on the sensor surface will experience a build-up of defects and suffer from the surface damage of the ionising dose, which could lead to a short circuiting of the  $n^+$ -strip implants. This is prevented using an inter-strip isolation technique based on p-stop traces, which was chosen out of several options tested on ATLAS07 devices. The sensor design also includes a protection structure for the AC coupling of the strips against beam splashes, a so called gated Punch Trough Protection [10]. The gated PTP design of the ATLAS12 sensors extends the strip below the bias resistor, leaving a  $20~\mu m$  gap to the bias rail and the gap covered by the extended sheet of the bias rail which results in a hard breakdown across this gap in case of an excessive potential.

Another novelty of the ATLAS12 is the staggered design of the bond pads to match the four rows of bond pads on ABC130 ASICS (see section 2.2.1) to facilitate wire bonding. The bond pad design in the sensor mirrors the bond pad arrangement of the ABC13 ASICS, which results in a four row bonding process, where each subsequent row increases in height.

During the development of ATLAS12 sensors, it was discovered that they were sensitive to humidity [11]. This meant sensor breakdown, indicated by high leakage current, at reverse bias voltages below the nominal operating voltage of -500 V was observed at ambient humidity levels. Therefore, a protocol was established over the course of the ABC130 barrel module program, which required a minimisation of sensor exposure to higher humidity levels to prevent early breakdowns:

- storage of sensors at modules at a maximum of 10 % humidity

- sensor tests to be performed at maximum relative humidity of 20 %

- minimisation of time sensors spent outside of dry storage, e.g. assembly

In addition to the construction of short strip modules, several long strip modules were constructed using ATLAS17LS sensors [12], which were developed after ATLAS12 sensors to prototype the long strip geometry. In contrast to the ATLAS12, the ATLAS17LS sensors are slightly larger with dimensions of  $98.0 \times 97.6 \, \text{mm}^2$ , utilising the full usable area out of 6-inch wafer. ATLAS17LS sensors have a strip pitch of  $75.5 \, \mu \text{m}$  and two long strip segments with 1280 4.83 mm strips each. Additionally, the wafer layout included new test structures and updated fiducial marks for spatial referencing for the ATLAS17LS design. The fabrication of ATLAS17LS sensors used split batches to test options for alternative passivation and a non-standard active depth [12].

#### 2.2 Readout chips

#### 2.2.1 ABC130

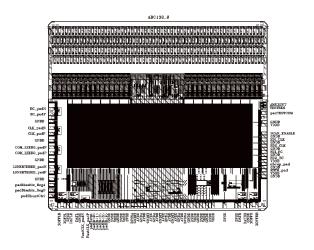

Each ABC130 chip [13] provides the initial data acquisition and readout chain for up to 256 sensor strips. Submitted in June 2013, it is the second generation of the ATLAS Strips readout family of custom Application Specific Integrated Circuits (ASICs) since the ABCD [14], which was used for the SemiConductor Tracker (SCT) readout. The ABC130 follows the ABCN-25 [15], which implemented ABCD in a new process, with some improvements, but kept a similar architecture. The ABC130 is the next member of this "ATLAS Binary Chip" family, and its suffix is from its implementation in IBM's (now GLOBALFOUNDRIES') CMOS8RF\_DM 130nm technology. The die has a size of  $6.8 \times 7.9 \text{ mm}^2$  with the wide side meant to be oriented orthogonally to the direction of the sensor strips and along the edge of the hybrid circuit board. With these dimensions, it allows for bonding of the input pads to the sensor strip pitch, while still allowing space for decoupling capacitors to be placed between chips.

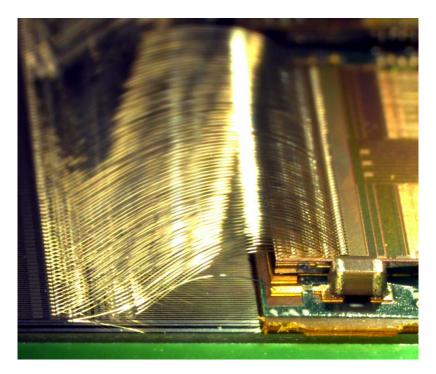

The first significant change from ABCN-25 is that the smaller feature size allowed a doubling of the number of readout channels per chip. The front-end input pads are arranged in a novel configuration of four staggered rows of 64 pads each (see figure 5b) for wire bonding to the AC sensor pads (see section 3.7). Ground pads at either end of each row provide for a sensor ground reference (HV decoupling and guard ring). The pitch of  $119 \, \mu m$  is chosen to allow direct bond connection from the available pad sizes to the sensor pitch. These pads are arranged so that one

(a) Pad layout of ABC130\_0 die (the ABC130\_1 die is a superset, see section 2.2.1.3).

**(b)** Photograph of ABC130 die showing I/O and four rows of front-end pads.

Figure 5. ABC130 die layout.

ASIC can be connected to two rows of strips on the sensor, with the edge of the ABC130 placed close to the boundary. The connections from both strip rows to the ASIC amplifier channels are interleaved, which provides a powerful performance cross-check in case of problems. These two rows are referred to as outer (running away from the ASIC) and inner (running under the ASIC). The outer strips are also connected by long bonds that reach over the top of those for the inner strips (see figure 39). Power and signal connections are restricted to the other three sides of the die and are wire-bonded to the hybrid circuit board (see section 3.1).

Another substantial change over the ABCN-25 is in the readout system. It was substantially updated and new trigger levels have been added in order to raise the trigger rate from 100 kHz to 500 kHz, and to include the regional readout concept [5]. The new architecture has three main stages:

- First, the inputs are sampled from the front-ends on every cycle of the LHC Bunch Crossing (BC) clock (40.079 MHz), and put into a synchronous pipeline (the "L0 buffer"). This allows an external process (the L0 trigger) up to  $6 \,\mu s$  to choose which crossings to read out, with  $1 \, BC = 25 \, ns$ ;

- When the L0 accept (L0A) arrives at the ABC130 (a fixed period from the original BC), the appropriate data is copied to the "L1 buffer";

- The final readout command (either R3 or L1A, described below) can then be received up to 512 μs later, and refers to a specific location in the buffer.

This architecture allows collection of data into the L1 buffer at a higher rate than the output bandwidth allows, as not all data might be selected for read out. The Regional Readout Request (R3) trigger is designed to be acted on by a small proportion of modules, selectable at the HCC-level (see section 2.2.2), based on where that module is in the detector, and provides fast readout of data that can provide input to the L1 Trigger system [5]. This proportion is expected to be no more

**Figure 6.** ABC130s are connected in daisy-chains of 5 ASICs, with each end of the chain connected to an HCC130 to allow bidirectional access to the chain in the event one of the ABC130s fails [5].

than 10% of the strip tracker on average. The L1A is then used to read out full information for the required BCs.

All digital signalling is carried out using SLVS [16] differential I/O between ABC130s and an HCC130 (see section 2.2.2), in a bi-directional daisy-chain fashion (see figure 6). This allows for the failure of individual ASICs as the readout direction from downstream ASICs in the chain can be reversed.

**2.2.1.1 Analogue front-end.** The ABC130 analogue front-end block consists of 256 independent input channels accepting negative signals from the AC-coupled n-type strips of the ITk strips sensor. The architecture and performance of the individual front-end channels are detailed in [17]. Each channel's preamplifier is designed around a single-ended buffered telescopic cascode with an NMOS input transistor. The input transistor is surrounded by the active feedback built with a PMOS transistor biased in saturation. This feedback scheme allows for full control of the DC potential at the preamplifier output and permits the use of a very power-efficient shaper stage with a single-ended input. This particular configuration of the input stage was originally designed for the p<sup>+</sup> on n sensors intended for the ATLAS tracker upgrade and was later modified for the negative-going signal of the current n<sup>+</sup> on p sensor. On the ABC130, the input current from the sensor strip to the input channel modulates the transconductance of the feedback transistor and causes degradation of the noise performance for negative and positive signals. These issues, as well as degradation of the noise performance after irradiation, have been addressed in the new design implemented for the ABCStar [18].

The preamplifier input stage has been optimised for the value of 5 pF, covering the expected range of input capacitance of the short strip (SS) sensors, but also operates effectively with the higher capacitance of long strip sensors (LS) as well as the different end-cap sensor configurations. This includes the expected parameter variation to maximum lifetime irradiation of the modules. The inputs are protected with non-silicided NMOS thin oxide devices, whose width was chosen as a tradeoff between ESD protection and the parasitic capacitance it added to each channel ( $\sim 0.4 \, \text{pF}$ ). The circuit was designed to withstand a 1.5 kV Human Body Model event and a 0.6 A Transmission Line Pulse (5 ns rise time, 100 ns duration). Therefore, a series 22  $\Omega$  resistor is used to improve response to the Charge Device Model, a tradeoff between protection and added noise. Inputs can be left unconnected without affecting the performance of any other channel.

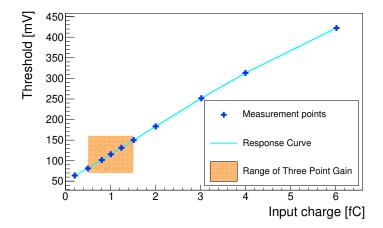

The effective channel gain is 80 mV/fC at nominal bias currents and process parameters with a signal response peaking time of around 22 ns. The Full Width at Half Maximum (FWHM) of the response is around 35 ns and the overall shaping function is close to a second order CR-RC filter. In terms of frequency response, if the AC-coupling between booster and shaper as well as the limitation of the preamplifier bandwidth are neglected, the front-end channel can be approximated by a bandpass filter with a center frequency of about 15 MHz and a roll-off of around 20 or 40 dB/decade for frequencies below or above, respectively. The time walk of the discriminator is below 16 ns for nominal threshold settings and 50 % of a minimum ionising particle's (MIP) signal after the total expected radiation dose.

This timing performance guarantees correct data association to a given BC for the worst case of signal charge sharing, where the charge is shared equally between neighbouring strips, and at the end of lifetime of the experiment. The response linearity is better than 5 % for signal charges from 0 to -4 fC, and better than 15 % from 0 to -8 fC. Expected noise is  $850\,e^-$  for SS sensors, and  $1150\,e^-$  for LS sensors. Double-pulse resolution for a -3.5 fC signal followed by a -3.5 fC signal is  $\leq 75\,\text{ns}$ , and maximum recovery time for a -80 fC signal followed by a -3.5 fC signal is 200 ns. For a -1 fC signal, the gain sensitivity to power supply voltage is  $< 1\,\%$  per  $100\,\text{mV}$ . The chip features a low dropout (LDO) linear voltage regulator that, in addition to improving the rejection of power supply noise at the front-end and providing an accurate voltage to the chip independent of any voltage drops on the hybrid, allows the analogue core operating voltage to be set to within  $\pm 20\,\text{mV}$  of the target voltage of 1.2 V. In addition, the preamplifier input transistor and feedback bias currents can be tuned to compensate for process variation with internal 5-bit Digital-to-Analogue Converters (DACs) referenced to an internal bandgap circuit ( $592 \pm 40\,\text{mV}$ ).

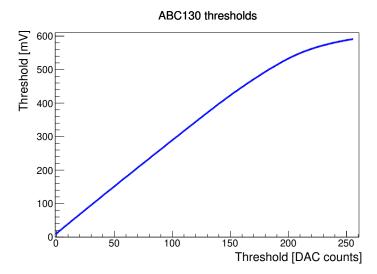

A common threshold level is set with an on-chip 8-bit DAC and is distributed to the 256 input channel discriminators by means of current mirrors. Due to process variation, there is about 20 mV rms of threshold variance between channels, so a 5-bit TrimDAC is provided for each channel. The magnitude (range of the DAC) of this tuning can also be adjusted. In this way, the inter-channel threshold variance can be reduced into the single millivolt range (see section 3.2.6).

The output of the threshold comparators is then sampled on the rising edge of the BC clock and shifted into the L0 Buffer (FIFO). A mask register is supplied to force a zero into the pipeline and allow skipping of any noisy channels.

Each channel includes the ability, selectable by a calibration enable bit, to inject a tunable calibration pulse to simulate a strip "hit". This capability can be used to calibrate the full tracker or a module performance on a per-strip level or as a Built-In Self-Test (BIST) function for the

inputs during testing of wafers. Each channel receiving a calibration pulse is connected to a 60 fF  $\pm 1$  % capacitor ( $\pm 10$  % over full production skew) through a CMOS switch. The injected charge is defined by setting a defined voltage using an 8-bit calibration DAC. A fixed-width calibration pulse (8BC  $\approx 200$  ns), generated by a chip-control command, activates a chopper circuit that applies the voltage to provide a controlled amount of charge (0 to -9 fC) to the input of each channel where the calibration pulse is enabled. The polarity of the calibration pulse is also controllable by a bit in the control registers. The relative phase of the calibration pulse can be varied using a programmable strobe delay circuit from 0 to 80 ns so the position of the pulse relative to the BC can be tuned for optimal results.

**2.2.1.2 Power and ground.** The ABC130 has independent digital and analogue power domains, each with its own power (DVDD and AVDD) and ground (GNDD and GNDA) pad connections, and each has its own on-chip programmable Low-DropOut (LDO) regulator that can be used to provide the required regulated +1.2 V core voltage. Options were also included on the chip to allow for the application of the core voltages using external connections. By providing a sufficient number of power pads connected to the outputs of the LDOs (VDDD and VDDA) that are normally connected to decoupling capacitors, these could also safely be used as power inputs if the LDO's input pads are not being powered. Furthermore, a voltage-controlled high current shunt circuit was included to allow for series powering of the chips. All of these modes of powering the ABC130 were tested, and it was decided to use the LDOs as voltage regulators to provide core voltages for both the analogue and digital portions of the chip when used on modules.

As part of the front-end pads array, there are four ground pads on each end to provide a ground reference for the sensor's HV decoupling and guard ring. Furthermore, there are three special sets of ground pads: analogue ground pads specifically for the front-end (GNDIT), and one pad each for the digital and analogue ESD circuit returns. On modules, all of these are wire-bonded to the respective digital or analogue ground planes of the hybrid.

The LDOs can be controlled by programming registers: each has its own Control Enable Bit and a register field that allows them to be tuned to  $1.20 \pm 0.02 \, \text{V}$  in 16 steps. If the Control Enable Bit is not set, then the output voltage of the LDOs (VDDD and VDDA) applied to the chip's core are the voltages applied to their inputs (DVDD and AVDD) minus the minimal drop across the LDOs. The chip is fully functional in this state; however, the LDOs should be tuned to  $1.2 \, \text{V}$  for proper operation during data taking. In addition to the programmable control, the chip has dedicated pads that can be used to disable the LDOs in case the chip is to be powered by externally provided core voltages or using the shunt circuit. The default state on power on with no connection to the pads is to have the LDOs disabled but controllable.

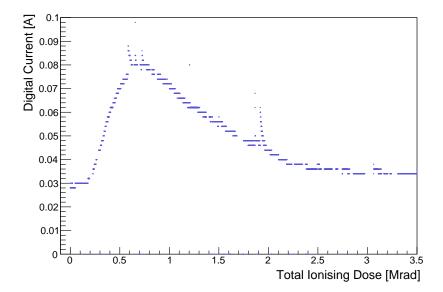

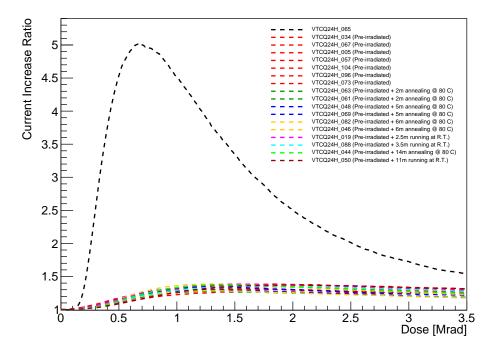

The nominal pre-irradiation current at  $+1.2\,\mathrm{V}$  is 40 mA for the digital portion of the chip, and 70 mA for the analogue circuitry. However, due to the Total Integrated Dose current "bump" (TID bump, see section 4.10) experienced by this CMOS technology, the amount of digital current drawn by the chip will increase by a factor  $O(100\,\%)$  with increasing radiation dose before falling back to near pre-irradiation levels as the dose moves out of the TID bump range (around 1 Mrad). To allow data taking to be consistent before, through, and beyond the TID bump operating region, the shunt circuit can be used to draw the difference between the expected maximum TID bump current, and the current being drawn by the chip at the current TID. As the current increases

through the TID bump, the shunt current can be reduced so the overall current remains constant. Similarly, the shunt current can be increased again as the TID bump current begins to decrease, again maintaining a constant operating temperature and current draw as the TID increases, and helping to ensure comparable results for measurements taken throughout the irradiated operating regions of this CMOS technology. For the next chip generation, the ABCStar, a procedure for its pre-irradiation has been developed to pass the TID bump before the ASICs are assembled into modules. The shunt circuit is disabled by tying the Shunt Control analogue input to ground.

**2.2.1.3 Digital input and output.** There are two types of digital I/O pads on the ABC130: low-voltage single-ended CMOS I/Os for low speed signals (LVCMOS [19]), and high-speed differential SLVS I/O with a nominal 600 mV common-mode voltage and 400 mV differential voltage (SLVS [16]).

Generally, static I/O uses the low-voltage CMOS single-ended signalling, and all clocks and data I/O use high-speed differential SLVS signalling. Most LVCMOS I/O is left without wirebonds when assembled onto a module, with the exception of the RSTB, and a 5-bit Chip ID (see section 3.1). Clock and command lines are implemented in a common-bus multi-drop configuration on the hybrids. Any command communications to the ABC130s contain a Chip ID and are only acted on by the chip whose ID matches the one in the command (with the exception that ID = 31 is a broadcast address and all ABC130s must respond to those commands). Similarly, all packets output by an ABC130 include its Chip ID to allow any packets it generates to be associated with that particular chip. Chip IDs only need be unique within a group of ABC130 ASICs read out by the same HCC.

In addition to the LVCMOS signals used during operation on a module, a number of other pads were provided as experimental features, as risk mitigation, or to assist in testing die before dicing the manufactured wafer of dice. These include:

- pads to disable the digital and/or analogue LDOs (active high with CMOS pull-downs)

- a Termination Enable pad (active high with a CMOS pull-down) that can be used to provide on-chip  $75\,\Omega$  (82  $\Omega$  max.) termination for the SLVS receivers

- the "abc up" pad (active high with CMOS pull-down) that can be used to invert the sense of the internal reset tree

- 5 pads to implement a JTAG [20] test interface (Scan\_Enable, SDI\_CLK, SDI\_BC, SDO\_CLK, and SDO\_BC).

The ABC130 will operate properly with any or all of these pads left unconnected.

All dynamic operations of the chip use high-speed differential SLVS I/O (each logical signal has both a positive and negative pad to provide differential input, output, or I/O as appropriate):

- two clock inputs, BC and RCLK (Readout CLocK)

- two command and trigger inputs, COM\_LO and L1\_R3

- a set of bi-directional data and flow-control signals: one set for the "left" side of the chip, DATAL and XOFFL; and one set for the "right" side of the chip, DATAR and XOFFR

The 40 MHz nominal differential BC clock is provided to all the ABC130s on a module via the HCC130 and is used to trigger sampling of the front-end inputs. The BC is also used as the clock for both the COM\_L0 and L1\_R3 differential Dual-Data Rate (DDR) inputs with effective input data rates of 2 times BC (80 Mbps nominal). Each input is split into two 40 Mbps signals. On the rising edge of BC, the COM\_L0 is latched as the command data stream to the ABC130s; and on the falling edge of BC, that signal is latched as the L0 trigger. Similarly, the L1 trigger data stream on L1\_R3 is latched on the rising edge of BC, and the R3 trigger data stream is latched on the falling edge of BC. Finally, the HCC130 provides the differential RCLK signal at up to four times the rate of the BC (160 MHz nominal) that is used to clock data on the DATAL/R digital readout pads and the XOFFL/R flow-control pad signals.

The bi-directional signals are configured in pairs, so that when DATAL is an output, DATAR is an input and vice versa. Similarly when DATAL is an output, XOFFL is an input and vice versa as in table 1. A single configuration register bit determines whether the ABC130 is operating in a "right to left" mode or in a "left to right" mode. When configured as outputs, the differential output current of the drivers are programmable between 1 mA and 7 mA, in 8 steps.

**Table 1.** Bidirectional signals, which side of the ASIC they are positioned, and whether they are inputs or outputs.

| Signal | Side of ASIC | I/O in L-R | I/O in R-L |

|--------|--------------|------------|------------|

| DATAL  | Left         | Input      | Output     |

| DATAR  | Right        | Output     | Input      |

| XOFFL  | Left         | Output     | Input      |

| XOFFR  | Right        | Input      | Output     |

When in "right to left" mode, DATAR is an input and forwards data received from its neighbour to the right through to DATAL. XOFFL is an input (recieving flow-control signalling from its neighbour to the left) and XOFFR is an output (providing flow-control to its neighbour to the right). When in "left to right" mode, the data, flow-control, and I/O directions are reversed. The ABC130s on a module are connected in a daisy-chain with the DATAR and XOFFR on one chip connected to the DATAL and XOFFL of the next chip to its "right". The farthest "left" and farthest "right" ends of the daisy-chain are connected to the HCC130 (see section 2.2.2), which can receive data and/or provide flow-control signals from either of the ends of the daisy-chain. This architecture allows part of the daisy-chain to be configured as "left to right" and the other part as "right to left" to handle the case of a single failed ABC130 anywhere in the daisy-chain. All chips to the "left" of a faulty ABC130, if any, are configured in the "right to left" direction; and all chips to its "right", if any, are configured in the "left to right" direction. This way, maximal physics data can be read out from a partially operational module (see figure 6).

The ABC130 was manufactured on a Multi-Project Wafer (MPW) run along with an unrelated chip. There were two different versions of the ABC130 in each reticle on the wafer: the ABC130\_0 and the ABC130\_1, which were identical in function except the ABC130\_1 additionally had experimental circuitry for a Fast Cluster Finder (FCF) and additional pads to support that functionality. The FCF was designed to provide prompt, BC-synchronous, cluster position data to an external device that could be used to correlate clusters between tracking layers and select high  $p_{\rm T}$  (transverse

momentum) coincidences to a trigger processing unit. Ultimately, this functionality was not used on the modules built with ABC130 chips, and was not tested during wafer testing either. The operation of this circuitry is beyond the scope of this article, but can be found in the ABC130 Specification [13].

**2.2.1.4 Chip operation.** For normal operation, after the chip is reset, the registers on each ABC130 are initialised using the command stream of the COM\_L0 DDR input with the values that have been determined to provide it with nominally tuned settings, and to set all relevant mode bits necessary to put the chip into the desired operational configuration. These settings include:

- the LDO tuning value required to provide 1.2 V core voltages to the analogue and digital circuit domains

- all of the front-end control DACs and TrimDACs to correct for process and inter-channel variation

- the channel mask registers to disable any known faulty input channels

- the required SLVS driver currents

- and the threshold value.

Setting the threshold to an optimal value for each ABC130 — which is distributed to all of its 256 input channels, each of which is fine-tuned by the per-channel TrimDACs — is critical, as it determines the front-end's sensitivity to signals from the sensor strips it is reading out, and its susceptibility to noise from the sensor and the front-end circuitry. The threshold can be set based on the requirements of a particular data-taking session and determines the "hit" rate (which can include both signal and noise), and thus the maximum data transmission bandwidth from the module during operation. There are features that can limit the maximum data rate of the ABC130s, but using these results in the discarding of potential hits (see below).

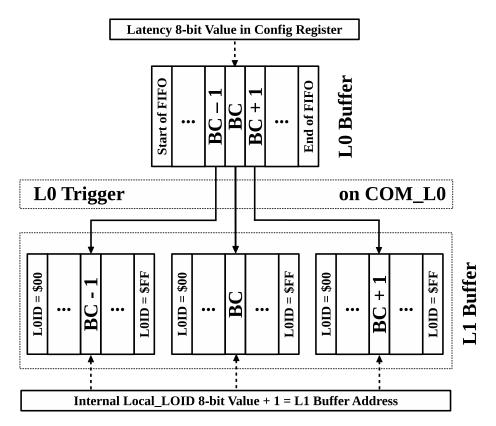

The decision to record a hit or no-hit is taken on the rising edge of the BC clock. The state of all 256 input channels of every ABC130 on a module will be sampled into its L0 Buffer, a 256 bit-deep FIFO. The state is formed by the logical AND of the input comparators reading out the sensor strip it is wire-bonded to, and the inverse of the associated Mask Registers bits (a 1 bit in a Mask Register will force its associated channel to always read as the 0, or "no hit", state). Each of these 256-bit input vectors is pushed from the front-end onto the L0 Buffer FIFO along with the value of an 8-bit, command resettable, BC counter (BCID). Because this process is continuous, a sample will remain in the L0 Buffer to be read out for a maximum of 6.387 µs before falling off the far end of the FIFO.

The next step is to capture the data from the L0 buffer into the L1 buffer. To save input vectors for possible later readout, an L0 (first level) trigger accept needs to be issued. This L0A is actioned by logic-level 1 on the COM\_L0 DDR input. When an L0A is received, one "event" from the L0 Buffer is transferred to the L1 Buffer. The Latency is the fixed number of BCs between when the front-end is sampled and when an L0A is received by the module from the trigger system to store that sample. This is configurable by the setting of the 8-bit Latency value in the chip's control register set, and specifies the address in the L0 Buffer of the centre of a 3-BC long "event". As shown in figure 7, an entry in the L1 Buffer consists of three 256-bit memory blocks, which will be

Figure 7. Transfer of event from L0 Buffer to L1 Buffer on receipt of L0 Trigger on COM\_L0 input.

used to store the L0 Buffer entries for: the previous bunch crossing, the bunch crossing of interest, and the next bunch crossing. All three of the values copied to the L1 Buffer (both the 256-bit input vector and the associated 8-bit BCID) will further be tagged with an 8-bit Local L0 IDentifier Counter (Local\_L0ID Counter) value. This whole event is stored at the address in the L1 Buffer specified by the Local\_L0ID Counter after it is incremented by one. Like the BC Counter, the Local\_L0ID Counter is settable to a known initial value (usually \$FF) when data taking begins so both the trigger system and the ABC130s are in synchronization and the first L0 Trigger writes into location 0 of the L1 Buffer. Since the L1 Buffer can store 256 entries, for a 500 kHz L0 Trigger rate, for example, it can hold the data for an event for 512 µs before it is overwritten with another event.

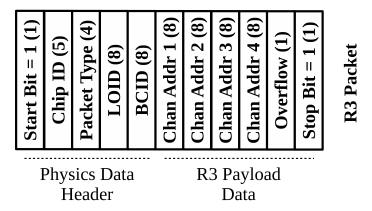

The final stage is to read out the event data from the L1 buffer. To read out the physics data of an event, an L1 or R3 Trigger is issued by the trigger system via the L1\_R3 DDR input (through the HCC130). Each of the trigger commands consists of a three-bit header — 110 for L1 and 101 for R3 — followed by the 8-bit L0ID value of the event to read out. The L0ID value sent with the trigger is simply the number of L0As sent since the Local\_L0ID counter was reset, and corresponds to the memory address of the L1 Buffer that will be read out. Depending on whether an L1 or R3 Trigger was issued, the event is sent to the L1-DCL (Data Compression Logic), or the R3-DCL, which generate a sequence of fixed length data packets.

The R3-DCL produces only a single output packet, and is intended to provide a quick snapshot of whether or not any clusters were detected for a particular bunch crossing event. Conversely, the L1-DCL produces a comprehensive output of all cluster data for the relevant event where the hit

**Figure 8.** Format of Regional Readout Request (R3) ABC130 Output Packet, the number in parenthesis indicates the corresponding number of bits.

data matches a specified pattern, and can result in many packets being queued for transmission. Both DCLs find clusters of hits, by searching the channels first in one set of 128 channels followed by the other 128 channels. Thus clusters are found only between strips in the same sensor region. Also, it does not "wrap" from one set to another. These are recorded in the output packet as 0-127 and 128-255.

For an R3 Trigger, the R3-DCL will generate a single output packet flagging whether there are no hits, some hits (1-4), or many hits (more than 4). The R3-DCL can be configured through the "EN\_01" bit in the configuration registers to either define a "hit" by looking for a hit only in the L1 Buffer block corresponding to the selected BC (level mode), or to look for a level change from 0 to 1 between the previous BC and the selected input vector (edge mode). The R3-DCL only registers clusters that have hits in a maximum of three channels, larger clusters are ignored. The location of the first hit is reported for clusters with width of 1 or 2, and the location of the central strip when the cluster width is 3. The R3-DCL will report the locations of a maximum of 4 hit clusters per event, and will set an overflow bit in the output packet if there are more than 4 valid clusters [13]. The format of the R3 packet is detailed in figure 8.

For an L1 Trigger, the L1-DCL reports clusters in one of two formats as selected by the "mcluster" bit in the configuration registers: either L1-3BC mode where information on all 3 recorded BCs are reported; or L1-1BC mode, where only cluster patterns are reported (see figure 9). For both modes, a compression mode can be configured to choose which clusters to report based on the pattern of bits in the 3 recorded BCs. There are two patterns for use during normal data taking, X1X (level) and 01X (edge), where the X indicates "don't care". A further "any hit" mode to be used for detector alignment matches (1XX or X1X or XX1). A final XXX mode is intended only for chip testing. Clusters are scanned for in the two sets of 128 channels based on this mode and clusters formed. When a hit is found that matches the selected pattern, that bit forms the first bit of that cluster and its location is used to report the start of the cluster in the packet. For the L1-3BC mode, that location is used as the channel address reported in the packet. The address is followed by the 3 bits for the hit on that channel (from the 3 recorded BCs), and the next three channels (whether or not they have any hits in them). The DCL then moves to the following channel to check for a new cluster start. Because 4 channels are reported per L1-3BC packet, a total of 64

**Figure 9.** Format of Second Level (L1) Trigger ABC130 Output Packets [number in parenthesis is number of bits].

packets could potentially be created if at least every 4th channel had a hit to cause a cluster to be reported. For the L1-1BC mode, up to three clusters can be reported: each one comprised of the 8-bit cluster start location, and the one-bit hit status of the following three channels (3 bits) based on whether that channel matched the hit criteria. Like the L1-3BC mode, the next cluster is searched for after the last bit of the previously reported 4 channels of cluster data. Because 3 clusters can be reported in each packet, up to 22 L1-1BC packets could be generated if every 4th channel had a hit to cause a cluster to be reported. It should be noted that due to the potentially large number of packets generated for an L1 Trigger event with many hits, the possibility of saturating the front-end circuitry with noise or hits from the sensors when the thresholds are set low needs to be managed carefully. If a large number of hits are expected, the L1 Trigger rate needs to be controlled carefully to ensure no loss of data in those situations. A further feature is provided in the ABC130 that allows the number of packets generated to be capped at some specified number less than 64 for L1-3BC mode or 32 for L1-1BC mode. While this mode could result in data loss, the assumption would be that the high-occupancy data is not useful.

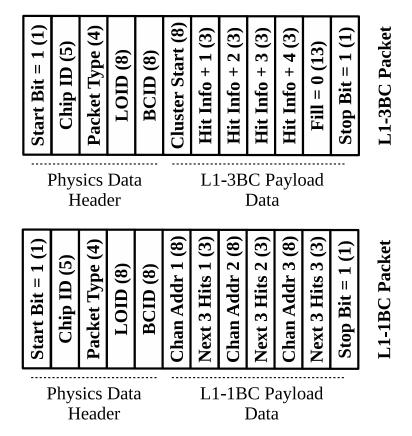

As packets are created by the DCL, they are pushed onto the appropriate flow-controlled FIFOs and are then pulled from the FIFOs and serialized according to their relative priority. In addition to FIFOs for the L1-DCL and R3-DCL, there is a FIFO to queue configuration register reads, and a separate FIFO to output the reading of a special high-priority status register (Register \$3F). These

Figure 10. ABC130 Packet Output Multiplexer with Priority Control.

are output in order of highest to lowest priority: high-priority register reads, R3-DCL, L1-DCL, and then regular register reads at the lowest priority. Furthermore, packets that are being transmitted through the ABC130 from an adjoining ABC130 or HCC130 are interleaved into the output data stream based on the setting of 4 Pry (priority) bits in the configuration registers. If there are packets from the internal data sources to send, Pry sets the number of through-packets that might be forwarded before one internally generated packet needs to be sent. Thus, if Pry is set to 0, then a through-packet will always be sent before any internally generated packets. If Pry is set to 8, for example, then 8 through packets (if present) will be forwarded before sending the next internally generated packet. If the through-packet FIFO (which is 4 deep) is about to be filled, the XOFF signal is asserted to the upstream chip to prevent the FIFO from overfilling and for through-packets to be lost that way. Similarly, if the internal FIFOs are about to fill up, the blocks that are sending data to them receive internal flow-control signalling and must stop operation until FIFO space is available for them to continue sending (see figure 10 on the FIFO and priority structure).

**2.2.1.5 Wafer testing.** Since ATLAS ITk strip tracker modules have up to 12 ABC-style chips connected to one HCC, if even one chip were to fail due to a manufacturing defect during module testing, it would require a risky and complex re-work effort to attempt to recover the module. While the data-flow architecture allows for the routing of data around a failed ABC130, 256-channels of data would still be lost. If that repair process failed or damaged the module, that one failed chip could result in the costly loss of an entire hybrid or module. As such, each ABC130 die undergoes an extensive testing and characterization process while still on the wafer using specialized wafer probing equipment and custom software. The ABC130s on the wafer are categorized into good (grade A), usable in the lab or in the event of a parts shortage (grade B), and bad dice (which can be used as mechanical samples for assembly testing and tooling development).

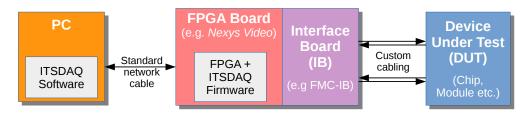

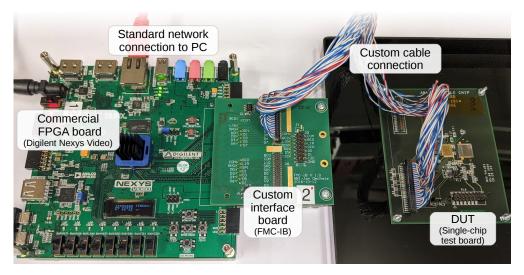

ABC130 wafer testing was conceptualised, developed, and implemented using a commercial semi-automated wafer-probing system, a commercially manufactured custom probe card, a custom

interface card and a commercial off-the-shelf (COTS) FPGA development board. The use of COTS components resulted in a much faster test system development compared to the custom electronics used for wafer testing during the construction of the ATLAS Semiconductor Tracker [21]. The wafer test software was integrated with the module test software suite: the ITk Strips DAQ (ITSDAQ, formerly SCTDAQ), see section 3.2.5. In the tests run on each ABC130 die on every wafer, the wafer is manually placed on the wafer-probing station's platen and positioned using the probestation's microscope's digital camera. Once the wafer is aligned, the wafer test software can step automatically between each of the ABC130s on the wafer and run all necessary tests on it.

The tests begin with basic integrity testing looking for gross failures of the die in terms of power supply currents and to ensure proper contact between the probe card and all of the die's pads. The tests then conduct a number of further sanity checks including:

- setting registers to default values and verifying that the power supply currents change appropriately

- tuning the chip's LDOs and front-end DACs

- scanning all other DACs

- a series of digital tests to check the functioning of the digital portion of the chip

- a series of complex functional tests are conducted to verify the chip's proper operation from front-end to data output

These final tests include tuning the chip's strobe delay value to provide optimal stimulus using the built-in calibration pulses, and then running a comprehensive 3-point gain test where each channel's front-end response to three different calibration pulse charges (0.5 fC, 1.0 fC, and 1.5 fC) is plotted to determine the gain response and noise level of all the input channels (see section 3.2.6). These tests also verify the functioning of triggering blocks, the L0 and L1 Buffers, the cluster finding and sparsification blocks, and the data transmission I/O blocks. The data is analysed in real time by ITSDAQ and the parts undergo a preliminary categorisation at that phase. Further analysis is performed offline on the data produced by the wafer probing routines where comparative analyses are also done between dice and between wafers, and the die categorisation can be updated as needed at that phase.

In preparation for the next generation chip, the ABCStar, and to ramp up towards full production testing, a second wafer test site was established. Whereas previously a system primarily developed in-house had been used for wafer testing, the second test site was established at an outside company to use their commercial, fully automated, wafer-probing stations and associated industrial test software infrastructure.

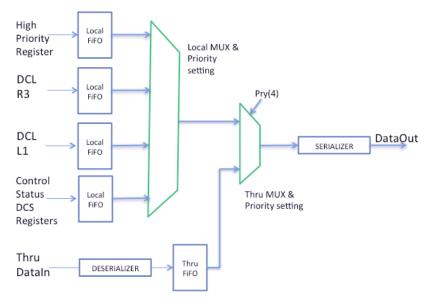

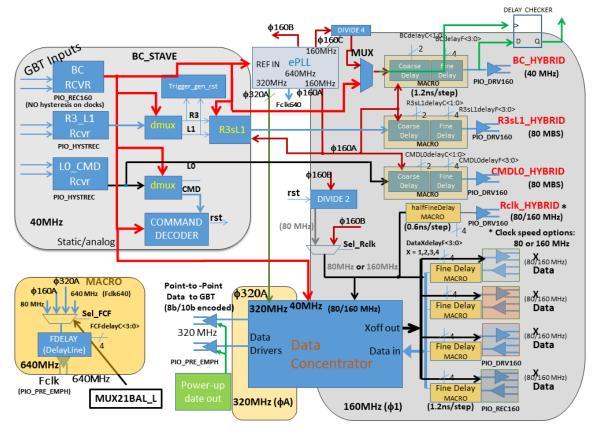

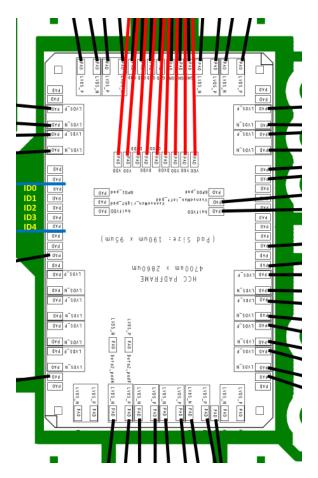

#### 2.2.2 HCC130

The Hybrid Chip Controller, HCC130, the first ATLAS strips prototype chip controller, was submitted for fabrication in August 2014. The 99-pad  $4.7 \times 2.96 \,\mathrm{mm^2}$  ASIC (see figure 11) was designed to provide the interface between the hybrid-mounted front-end ABC130 and the off detector electronics through the GBTx [22] using LVDS-like low voltage differential drivers and

receivers. It also contained an early version of the Autonomous Monitor that was functionally validated and eventually moved to the AMAC ASIC (see section 2.2.3). HCC130 receives the 40 MHz bunch crossing (BC) clock and two, custom protocol control signals from multi-drop buses driven by the GBTx. Both of these control signals are encoded with two independent logical streams time multiplexed into one. Data of all types sent from each module are transmitted point to point by the HCC130 to the GBTx at 160 or 320 Mbps.

The L0\_COM physical control signal encodes L0, a beam synchronous trigger that stores the ABC130 pipeline delayed data into a 256-word deep data buffer from which data are requested for readout. The second logical channel of L0\_COM signal is a priority based variable length Command (COM) protocol that provides control to set operational modes in both the HCC130 and ABC130 ASICs and initiates requests for data from internal registers in the HCC130 and ABC130 ASICs. The difference in naming from the ABC130 indicates a subtle difference in that the HCC130 modifies the COM signal before forwarding to the ABC130, to mask out commands intended for ABC130 attached to other HCC130 on the same bus.

The R3s\_L1 physical signal provides two triggers used to request readout of data from the ABC130. The L1 is broadcast directly to the ABC130s, requesting readout of data from one of the 256 memory locations of the ABC130s L1 buffer. In addition to the L0ID identifying the memory location to read out, the R3s signal contains an extra 14 bits, used to propagate the signal only to HCC130s with matching addresses. In this mode only addresses 2-29 are available. If the address matches, the mask bits are stripped and the remainder broadcast to the ABC130s.

The HCC130 utilises a copy of the CERN ePll block designed for the GBTx [22] to generate low jitter, 40, 80, 160 and 320 MHz clocks using the incoming multi-drop 40 MHz BC as a reference. The ePll is used internally on the HCC130 and provides the hybrid ABC130s with a regenerated, programmable, phase delayed 40 MHz clock for phasing event data properly within the beam crossings and related pipeline control. It also provides the ABC130s on the hybrid with a selectable 80 or 160 MHz data clock to drive the serial loops used for data readout. HCC130 can collect data from the hybrid through any of its four serial receivers attached to either end of the two hybrid readout loops. Corresponding XOFF signals allow for flow-control to the ABC130s. This readout technique provides contingency for single and multiple chip failures in either of the two ABC130 serial data loops. Once on the HCC130, a priority encoder ensures an even flow of data from the two ends of each loop and that R3 data are sent to the DAQ system with the highest priority. A data concentrator merges data from the two loops. A detailed HCC130 functional block description is shown in figure 12.

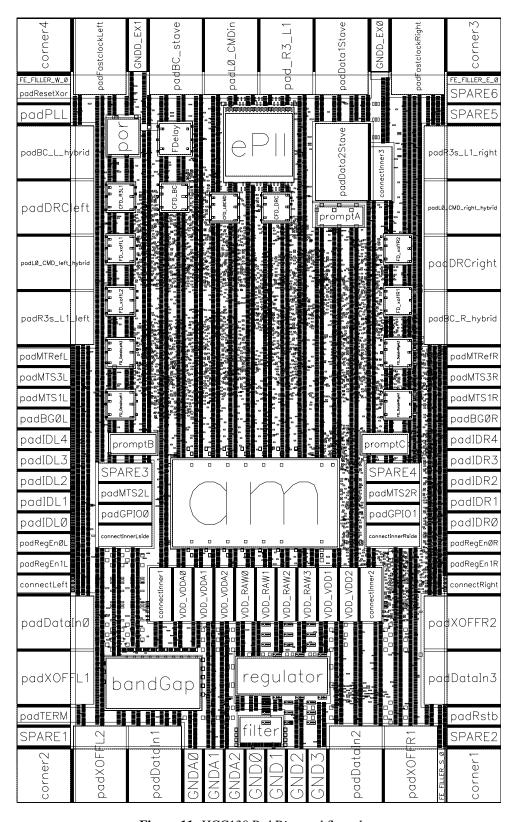

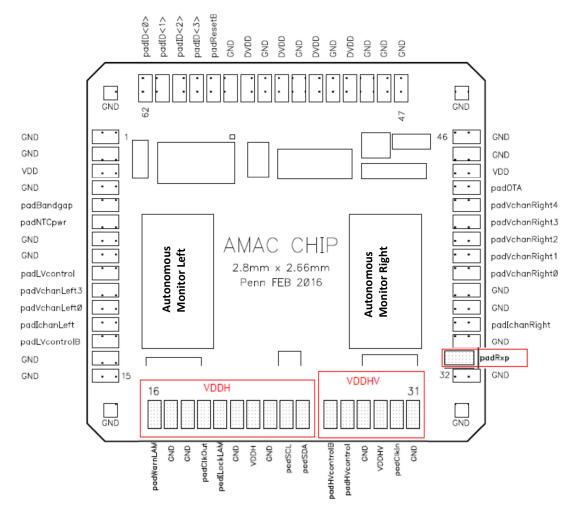

#### 2.2.3 AMACv1a

The Autonomous Monitoring And Control ASIC (AMAC) was submitted for fabrication in August 2016. It was the first successful prototype of the radiation tolerant, ten bit precision analogue monitor ASIC and was constructed using two identical seven channel Autonomous Monitor blocks originally housed in the HCC130. The AMACV1a pad frame is shown in figure 13: it has 62 bond pads and a die size of  $2.7 \times 2.8 \, \mathrm{mm}^2$ . An internal ring oscillator provides a near 40 MHz clock to control the autonomous monitor functions and I2C protocol is used for control and readout. AMACV1a monitors 14 independent module level parameters: voltages, temperatures and sensor leakage current. A clock driven state machine controls a switched capacitor stepped integration

**Figure 11.** HCC130 Pad Ring and floorplan.

Figure 12. HCC130 block diagram.

ramp to create a common reference for the Wilkinson style ADC. Each integration step increases the reference by 1 mV and increments a ten bit counter reset to 0, each 1023 step ramp cycle. Each of the 14 monitored parameters is translated into a voltage between 0 and 1 V and compared with the ramp that covers the same range. When the reference ramp exceeds the value of the measured parameter for two consecutive ramp steps the counter value is recorded in a register and compared with pre-programmed upper and lower limits. Out of limit values are flagged and — if enabled — can switch the state of four logic outputs that may be wired to LV or HV supply controls. Measured values are updated and stored locally once per millisecond. They may be readout remotely through the I2C interface.

#### 2.3 Hybrids

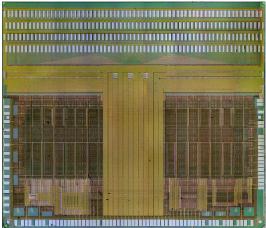

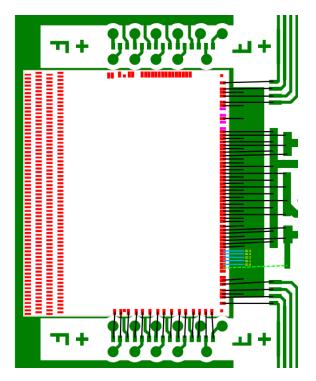

Readout chips for ABC130 barrel modules are mounted on flexible, radiation hard and low mass Polyimide circuits (called hybrids), which were developed to carry ten ABC130 readout chips and one HCC130 readout chip each (see section 2).

Hybrids provide the following electrical functionalities:

- Multi-drop external clock and control are connected to the hybrid

- On-hybrid internal clock and control are distributed to the ABC130 chips

- All ASICs on the hybrid are connected to a common ground and power domain

Figure 13. AMAC v1a Pad Ring and floorplan.

• Hybrid front-end data is returned to the high-level readout via the end-of-substructure card (see figure 1a)

The hybrid readout topology groups the ten ABC130 readout chips into two daisy-chains of five chips each. Each chain can be read out in either direction by the HCC.

ABC130 barrel modules are assembled by gluing hybrids with readout chips directly onto the surface of silicon strip sensors (see section 3.7). The circuit layout has been optimised to minimise electrical interference into the sensitive analogue front-end electronics or sensor strips. This has been achieved by the use of a single power and return domain with partioning of analogue and digital circuitry to mitigate common impedance coupling of the analogue and digital signalling. Furthermore, fast digital signalling within close proximity of the analogue front-end are routed as differential strip-lines to take advantage of the shielding effect of the return planes.

In addition to ABC130 and HCC130 readout chips, hybrids are equipped with two NTC thermistors, of which one is used to monitor the hybrid temperature during operation. The second one is part of a temperature interlock system required during the burn-in of hybrids as part of their quality control.

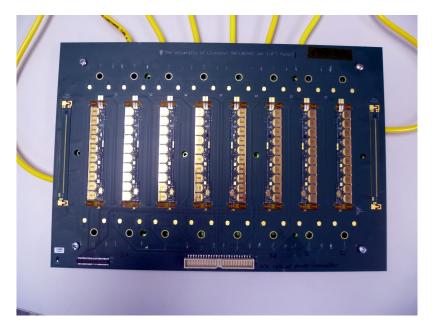

Figure 14. ABC130 barrel hybrid panel with four X-type hybrids, four Y-type hybrids and two test coupons.

In order to ensure a maximum yield, hybrids were designed to utilise standard manufacturing processes with long-term reliability. Tracks and gap sizes are about  $100\,\mu m$ , vias (plated laser drilled holes) have a hole diameter of about  $150\,\mu m$  and lands of  $350\,\mu m$ , which ensures uniform plating and therefore reliable contacts through vias. Barrel hybrids comprise three copper layers ( $18-35\,\mu m$  thickness) between polyimide dielectrics ( $50\,\mu m$  layer thickness), resulting in a total hybrid thickness of approximately  $300\,\mu m$ .

Hybrids are produced on panels (glass-reinforced epoxy laminate sheets) which hold four X-and four Y-type hybrids (see figure 14) as well as two test coupons per panel, which are used for hybrid manufacturing quality control:

- testing of via reliability by via chain resistance measurements

- monitoring trace etching quality by testing DC resistance of test traces

- testing quality of surfaces for wire bonding by performing wire bonding pull tests

Hybrid panels are equipped with vacuum holes and landing pads for assembling hybrids and readout chips (see section 3.1) as well as traces and connectors for the electrical testing of fully assembled hybrids (see section 3.3).

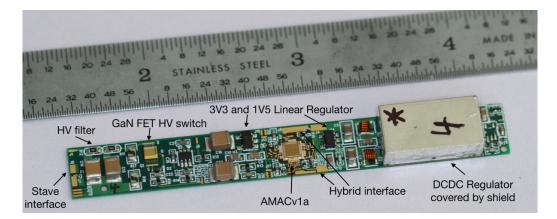

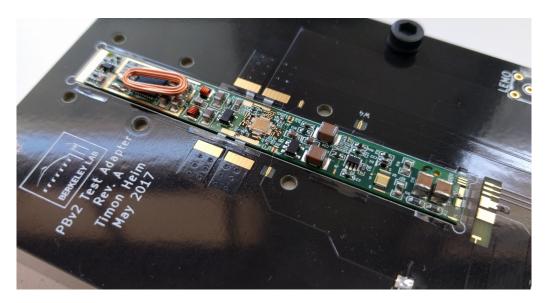

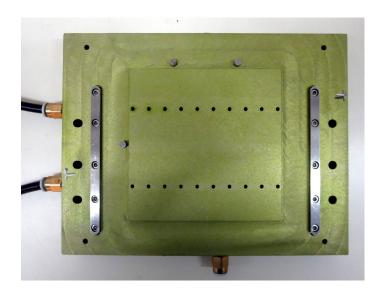

#### 2.4 Powerboard

The powerboard fulfils three purposes on the ITk Strip Module:

- 1. DCDC regulation of the 11 V input to 1.5 V to supply the ASICs on the hybrid

- 2. High-voltage switching of up to -500 V to reverse bias the sensor

3. Control of low-voltage and high-voltage supply, as well as monitoring of voltages, currents, and temperatures

The DCDC regulation is achieved by the FEAST chip [23], a radiation hard custom ASIC developed by the CERN electronics group for various experiments and their detectors. The FEAST employs a buck-converter style switching regulator, which requires an external inductance. For the powerboard, this inductance is an air-core solenoid coil with a nominal inductance of 545 nH and DC resistance of 35 m $\Omega$ . It is required to be an air-core coil as the detector will be placed in a 2 T solenoid field, which precludes the application of ferrite cores.

Due to the shape and characteristics of an air-core solenoid, during operation the coil emits RF noise, which could be picked up by the silicon strips underneath and around the powerboard. Therefore, the whole DCDC circuit is enclosed by a shield formed by a specific copper layer in the PCB underneath and a 100 µm thick aluminium shield-box soldered on top with continuous seams.

Switching control of the high-voltage is gained via a GaNFET transistor switch, by routing the high-voltage supplied to a module onto the powerboard through the switch. This routing also allows a low-pass RC-filter to be placed at the output of the high-voltage line, which is connected to the silicon sensor. To switch the GaNFET, a voltage of more than 2 V between gate and source is needed, as the source of the transistor after closing the circuit is at high voltage. An AC signal at a frequency of 100 kHz and amplitude of 3.3 V is AC-coupled into the high-voltage domain. It is then amplified and rectified via a quadruple charge pump circuit, which generates the necessary gate voltage with respect to the current source potential.

Both the low-voltage and high-voltage domain are controlled by the AMAC chip, which has been designed specifically for the usage on the powerboard. It can generate an enable signal for the FEAST chip to turn on the power to the 1.5 V domain and also generates the AC signal to switch the high-voltage on or off. Furthermore, the AMAC chip features multi-channel ADCs to measure multiple operation critical values:

- · input and output voltage and current

- FEAST internal temperature (via an internal PTAT circuit)

- powerboard temperature (via NTC thermistors)

- hybrid temperature (via NTC thermistors, for later powerboard versions)

- · and silicon sensor leakage current

It also contains logic to set an upper and lower boundary on the monitored values and if these limits are violated it can interlock the low-voltage or high-voltage of the module.

A picture of powerboard v2 can be seen in figure 15, which shows the main components of the powerboard. On this specific version of the powerboard the AMAC is powered via two commercial linear regulators, in the next version of the powerboard these will be replaced by a rad-hard linear regulator, the LinPOL12V, which will also be used in the final production version of the powerboard.

**Figure 15.** Photograph of a fully assembled powerboard v2. The main components of design are pointed out as well as the interface.

#### 3 Module construction

Each ABC130 barrel module consists of one sensor (see section 2.1), one or two hybrids (see section 2.3) with ten ABC130 chips and one HCC130 chip each (see section 2.2) and one powerboard (see section 2.4). Modules are assembled in a defined series of steps optimised for early defect detection to avoid the use of low-grade electronics on good quality sensors:

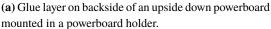

- 1. gluing readout chips to hybrids and powerboards (see sections 3.1 and 3.4)

- 2. electrical connection of readout chips to hybrids and powerboards using an automated wire bonding process

- 3. tests of electrical functionalities of hybrids and powerboards (see sections 3.3 and 3.5)

- 4. gluing tested hybrid(s) to sensor (see section 3.7)

- 5. electrical connection of hybrid(s) and sensor using an automated wire bonding process

- 6. electrical tests of module (see section 3.8)

- 7. gluing tested powerboard to sensor (see section 3.7)

- 8. electrical tests of module (see section 3.8)

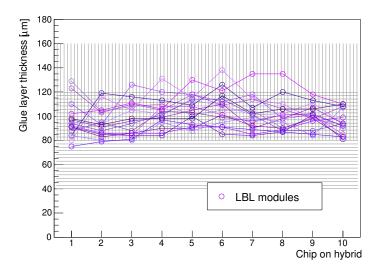

Components are mechanically and thermally connected using adhesives, which achieves the low material budget required in the ATLAS tracker [5]. Each hybrid and module is assembled in a manual process using custom designed precision tooling (see section 3.1) including a stencil to ensure a reliable glue coverage and thickness between components. After each gluing step, the glue thickness between components is checked by performing metrology measurements. Since the stenciling process ensured a consistent glue volume, glue layer thicknesses outside the specified range were found to lead to lower quality wire bonds:

thick glue layers, corresponding to low glue coverage under components, resulted in insufficiently supported bond pads and therefore weak wire bonds

**Figure 16.** Two hybrid flexes on a panel with pads for ABC130 chips (yellow) and one HCC130 (orange). Precision cut holes (blue) are used to position tools for population with ASICs. Landing pads (cyan) are used as height reference during ASIC population.

• thin glue layers led to glue covering wire bond pads and prevented electrical connections between bond pads and attached wire bonds and thereby caused electrical failures

Additionally, glue layers with insufficient height between hybrids or powerboards and sensors led to glue spreading towards the sensor guard ring area, which was found to result in early sensor breakdowns [24].

#### 3.1 Hybrid assembly

For the construction of hybrids, ten ABC130 readout chips and one HCC130 readout chip are glued onto an X- or Y-type flex in a series of manual steps that use precision tooling for positioning.

Prior to assembly, the involved components were tested for electrical functionality:

- · circuits on the flex were tested by the manufacturer

- ABC130 ASICs were probed on a full wafer of chips (see section 2.2.1)

- most HCC130 ASICs were probed, but after a high success rate during initial tests (97 %) and technical difficulties with the test setup, tests of individual ASICs were eventually stopped

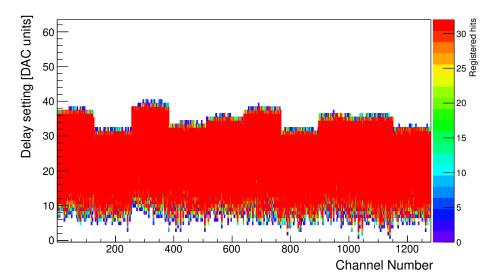

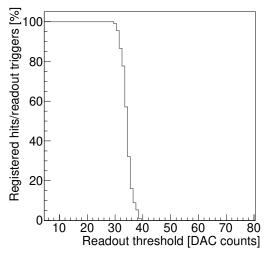

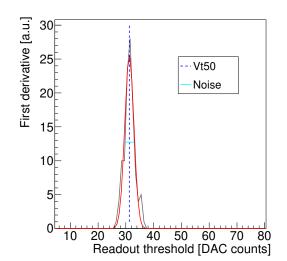

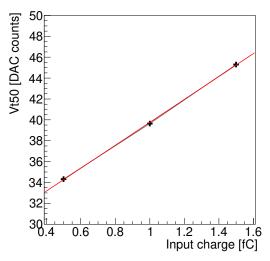

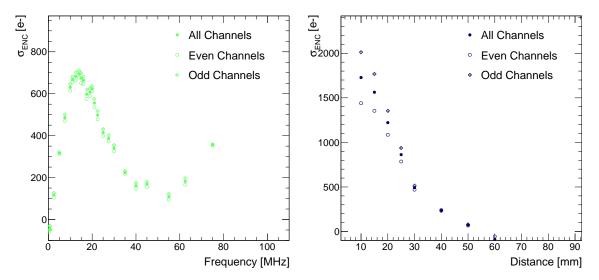

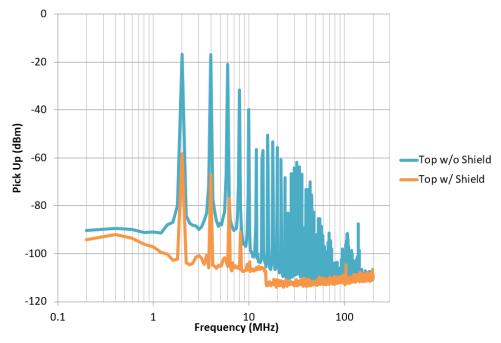

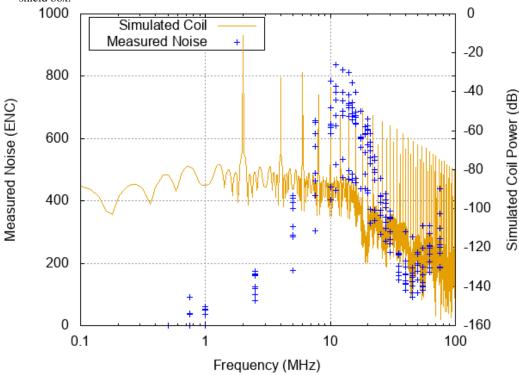

All components were handled in a cleanroom environment using vacuum tools to avoid contaminations prior to wirebonding (see below).