# The upgrade of the H.E.S.S. Cameras

Gianluca Giavitto<sup>a,\*</sup>, Terry Ashton<sup>b</sup>, Arnim Balzer<sup>c</sup>, David Berge<sup>c</sup>, François Brun<sup>d</sup>, Thomas Chaminade<sup>d</sup>, Eric Delagnes<sup>d</sup>, Gerard Fontaine<sup>f</sup>, Matthias Füßling<sup>a</sup>, Berrie Giebels<sup>f</sup>, Jean-Francois Glicenstein<sup>d</sup>, Tobias Gräber<sup>a</sup>, Jim Hinton<sup>g</sup>, Albert Jahnke<sup>g</sup>, Stefan Klepser<sup>a</sup>, Marko Kossatz<sup>a</sup>, Axel Kretzschmann<sup>a</sup>, Valentin Lefranc<sup>a,e</sup>, Holger Leich<sup>a</sup>, Hartmut Lüdecke<sup>a</sup>, Iryna Lypova<sup>a</sup>, Pascal Manigot<sup>f</sup>, Vincent Marandon<sup>g</sup>, Emmanuel Moulin<sup>d</sup>, Mathieu de Naurois<sup>f</sup>, Patrick Nayman<sup>e</sup>, Stefan Ohm<sup>a</sup>, Marek Penno<sup>a</sup>, Duncan Ross<sup>b</sup>, David Salek<sup>c</sup>, Markus Schade<sup>a</sup>, Thomas Schwab<sup>g</sup>, Rachel Simoni<sup>c</sup>, Christian Stegmann<sup>a</sup>, Constantin Steppa<sup>a</sup>, Julian Thornhill<sup>b</sup>, François Toussnel<sup>e</sup>

<sup>a</sup>DESY, D-15738 Zeuthen, Germany

<sup>b</sup>Department of Physics and Astronomy, The University of Leicester, University Road, Leicester, LE1 7RH, United Kingdom GRAPPA, Anton Pannekoek Institute for Astronomy, University of Amsterdam, Science Park 904, 1098 XH Amsterdam, The Netherlands <sup>d</sup>DSM/Irfu, CEA Saclay, F-91191 Gif-Sur-Yvette Cedex, France <sup>e</sup>LPNHE, Université Pierre et Marie Curie Paris 6, Université Denis Diderot Paris 7, CNRS/IN2P3, 4 Place Jussieu, F-75252, Paris Cedex 5, France  $^f$ Laboratoire Leprince-Ringuet, Ecole Polytechnique, CNRS/IN2P3, F-91128 Palaiseau, France <sup>g</sup>Max-Planck-Institut für Kernphysik, P.O. Box 103980, D-69029 Heidelberg, Germany

#### **Abstract**

The High Energy Stereoscopic System (H.E.S.S.) is an array of imaging atmospheric Cherenkov telescopes (IACTs) located in the Khomas highland in Namibia. It was built to detect Very High Energy (VHE, > 100 GeV) cosmic gamma rays. Since 2003, H.E.S.S has discovered the majority of the known astrophysical VHE gamma-ray sources, opening a new observational window on the extreme non-thermal processes at work in our universe. H.E.S.S. consists of four 12-m diameter Cherenkov telescopes (CT1-4), which started data taking in 2002, and a larger 28-m telescope (CT5), built in 2012, which lowers the energy threshold of the array to 30 GeV. The cameras of CT1-4 are currently undergoing an extensive upgrade, with the goals of reducing their failure rate, reducing their readout dead time and improving the overall performance of the array. The entire camera electronics has been renewed from ground-up, as well as the power, ventilation and pneumatics systems, and the control and data acquisition software. Only the PMTs and their HV supplies have been kept from the original cameras. Novel technical solutions have been introduced, which will find their way into some of the Cherenkov cameras forseen for the next-generation Cherenkov Telescope Array (CTA) observatory. In particular, the camera readout system is the first large-scale system based on the analog memory chip NECTAr, which was designed for CTA cameras. The camera control subsystems and the control software framework also pursue an innovative design, exploiting cutting-edge hardware and software solutions which excel in performance, robustness and flexibility. The CT1 camera has been upgraded in July 2015 and is currently taking data; CT2-4 have been upgraded in fall 2016. Together they will assure continuous operation of H.E.S.S at its full sensitivity until and possibly beyond the advent of CTA. This contribution describes the design, the testing and the in-lab and on-site performance of all components of the newly upgraded H.E.S.S. camera.

Keywords: H.E.S.S. upgrade, Atmospheric Imaging Cherenkov Telescopes, NECTAr chip, PMT readout

#### 1. Introduction

The four 12 m diameter Cherenkov Telescopes (CT1-4, [1]) of the HESS array started taking data in 2002. The first reason for upgrading their cameras is to reduce the rate of failures due to the ageing of the electronics, which have been operated continuously for more than a decade now. In 2012 a fifth telescope (CT5) joined the array. Due to its large mirror surface, its energy threshold is lower (~ 30 GeV), than that of CT1-4 alone (~ 100 GeV). This also implies that the trigger rate of CT5 is an order of magnitude higher than that of CT1-4, from 200–300 Hz to 1.5 kHz or more. Due to the relatively high dead time of the old cameras ( $\sim 450 \,\mu s$ ), when CT5 is included in the observations a substantial fraction of triggered events lose the

In order to fulfill the above goals, the upgrade of CT1-4 implied renewing the whole camera electronics, the cabling, ventilation, power supply and pneumatics. Practically all camera components except the photomultiplier tubes (PMTs) and the single photoelectron calibration unit have been replaced. The data readout of the upgraded cameras is built around the NEC-TAr analog memory chip [2], which allows for a much lower dead time with respect to the older system.

This camera upgrade will improve the performance of the HESSarray and is an ideal test bench for new technologies considered for the next generation Cherenkov Telescope Array.

CT1-4 information. Another main goal of the CT1-4 upgrade is therefore to reduce the dead time of the old cameras by two orders of magnitude.

<sup>\*</sup>Corresponding author: gianluca.giavitto@desy.de

#### 2. Camera components

Due to the scope of the upgrade and to manpower constraints, we used commercial, off-the-shelf components whenever possible. The custom-built electronic board types in the camera are 6 in total, 2 additional devices were developed for calibration and testing.

The devices developed for this upgrade (drawers, drawer interface box and power distribution box, described later) are equipped with ARMv5-based computer modules (Stamp9G45) running the Yocto embedded Linux operating system [3]. The ARM computer module communicates with an FPGA (Cyclone IV) over a 100MBit/s memory bus, and is equipped with an Ethernet interface connected to a central 10 GB/s switch. The camera slow control and the data readout are done over TCP/IP connections. This solution provides a flexible common architecture for the control of the camera. The presence of a computer on each device on the camera (62 in total) improves its resilence, because of three reasons: several security features can be implemented or made redundant by software running on it; it has the capability to buffer up to minutes of data; the Ethernet physical interface is managed by it and thefore there is no need to re-implement the TCP/IP protocol on the FPGA.

The most complex board designed for this upgrade is the so-called analog front-end board, which amplifies and digitizes the PMT signal. Each of these boards can read out 8 PMTs; two of them are connected to a slow control board, forming one 16-pixel modular unit called *drawer* (see Fig. 1 left). On the analog board, the PMT signal is split at the analog amplification stage in two branches: a readout branch, consisting of two signals with different amplification factors (15.1 for the high gain and 0.68 for the low gain), and a trigger branch, with amplification factor 45. The readout branch is fed to the NECTAr chip for sampling and digitalization; the trigger branch goes to a comparator, the output of which is the zeroth level (L0) of the trigger logic, and is routed to the FPGA on the slow control board. The main features of the front-end signal readout are summarized in Table 1.

Table 1: Features of the NECTAr chip

| Feature              | Value                     |

|----------------------|---------------------------|

| Sampling rate        | 1 GS/s                    |

| Sampling depth       | 12 bit                    |

| Dead time            | $\sim 5.5 \mu \mathrm{s}$ |

| Bandwidth            | 330 MHz                   |

| Pedestal noise       | 2 mV, (0.32 ph.e.)        |

| Linearity deviations | 2 %                       |

There are 60 drawers in the camera, forming the front-end electronics. Each of them has three connectors: one for power, one for trigger, and one for Ethernet. They are connected to the back-end electronic modules, which are located inside one 19 in. rack (see Figure 2). The 60 4-pole M8 power cables are connected to the *power distribution box*, a 24V power switch with monitoring and security features. The trigger cables are regular Ethernet cat 6a cable which carry 4 LVDS lines: a 10 MHz

Figure 1: An upgraded drawer. The analog front-end boards (vertical, left and right) are connected to the slow control board at the bottom. The NECTAr chips are the black square chips with the flower logo; the slow control board has test loads with green LEDs mounted at the PMT bases connectors. In the middle is the FPGA (black chip), and the green add-on board at the back is the ARM computer module.

clock, two trigger outputs and one trigger input. They are connected to the most important component of the back-end, the *drawer interface box*. This module is responsible for the clock distribution to the drawers, the GPS timestamping of events, the interface to the calibration units, the readout of auxiliary sensors to protect PMTs and camera electronics, the trigger interface to 60 drawers and to the array central trigger and, most importantly, the camera-wide (L1) trigger generation.

The L1 trigger logic requires the coincidence between *N* pixels inside one of the 38 overlapping 64-pixel sectors. The L0 signal is sampled at 800 MHz by the FPGA on the slow control board, and the number of pixels with L0 active for each analog front-end board is sent to the drawer interface box as an analog signal with variable amplitude and over one LVDS trigger output line. This signal is then summed with the others inside the trigger sector, compared to a common threshold and finally combined in an OR logic to give the L1 signal. The design is analogous to the original one, except for the fact that the L0 trigger comparator output is sampled by the drawer FPGA.

The upgraded camera is air-cooled as the original one, but instead of the many small fans previously mounted on the camera sides, the new cooling systems sports a single powerful ventilator located on the back door, which had to be renewed as well. The air intake is filtered by two sets of filters, and there is a heating system which can heat the air if it is too cold or too wet. The air is forced into the camera at a rate of  $> 360\,\mathrm{L/s}$ . This induces an overpressure inside the volume of the camera, forcing the air to flow through the drawers and keeping them at a temperature of  $\sim 32\,^{\circ}\mathrm{C}$ , with a gradient of  $\pm 5\,^{\circ}\mathrm{C}$  along the top-bottom direction. Due to its weight, the new camera back door is opened by a new pneumatic system consisting of two cylinders.

The camera network allows the main camera server to control drawers, drawer interface box, power distribution box and ventilation system. All camera subsystems also continuously send monitoring data via Ethernet. The main camera Ethernet switch is located inside the camera body, but the camera server is located in a server room in a separate control building, and connected to the camera by means of a 10 Gbit/s optical fiber

Figure 2: Left: Image of the back end rack. From top to bottom: Ethernet-controlled main power switch (1 unit at the very top), commercial 1-unit TDK Lambda 24V DC power supply, power distribution box (2 units), drawer interface box (3 units) 2 commercial 48-ports 10GB/s network switches, pneumatic control box. The red Ethernet cables are for the data network, the blue Ethernet cables for the trigger, the black cables for the power. Right: Picture of the power distribution box (top) and the drawer interface box (bottom), with their lids removed to show the boards inside.

connection. The slow control communication is implemented using the Apache Thrift framework [4], using the ØMQ [5] transport library as a backbone. The devices push the data over the network, being it raw event data or monitoring data. The former employ an optimized serialization protocol, whereas the latter are serialized using the Google Protocol Buffers library [6]. These open source, off-the-shelf technologies allowed the small team of software developers to develop a flexible, extendable and testable camera slow control and event acquisition software in a relatively short time.

## 3. Status of the upgrade and outlook

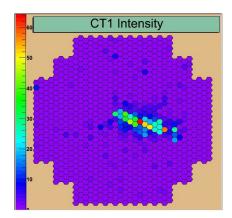

The upgrade had a two phases. During the first phase, only one camera (CT1) was upgraded, in July–August 2015, with the first gamma-ray shower images taken in August 2015 (see Fig. Fig. 3, right). The commissioning and debugging of this camera lasted until March 2016, when it started participating reliably in nightly data taking. The remaining three cameras were upgraded in September 2016 and are currently undergoing commissioning and fine-tuning, with some full array observations already underway. This staged approach allowed the smaller upgrade team to have a quick feedback on the operations of the camera from the larger HESScollaboration and to find and fix several problems found there before the installation of the other three. All parameters cited in this work have been cross-checked against the data produced by this first camera.

Figure 3: One of the first Cherenkov showers recorded with the upgraded camera

The HESS I Upgrade design offers the opportunity to optimise several aspects of the camera operation, for example to introduce different trigger logics, or take deep full-sampling runs, or store the arrival time information of the PMT pulses. These optimizations have the potential of further improving the sensitivity of HESS, beyond the upgrade original goals, and dedicated investigations towards this direction are planned.

Furthermore, the upgrade provides a test bed for various technical innovations that have been the subject of R&D efforts for the next generation of Cherenkov telescopes. Most importantly, it is the first major installation using the novel NECTArreadout and sampling chip.

### Acknowledgments

The support of the Namibian authorities and of the University of Namibia in facilitating the construction and operation of H.E.S.S. is gratefully acknowledged, as is the support by the German Ministry for Education and Research (BMBF), the Max Planck Society, the German Research Foundation (DFG), the French Ministry for Research, the CNRS-IN2P3 and the Astroparticle Interdisciplinary Programme of the CNRS, the U.K. Science and Technology Facilities Council (STFC), the IPNP of the Charles University, the Czech Science Foundation, the Polish Ministry of Science and Higher Education, the South African Department of Science and Technology and National Research Foundation, and by the University of Namibia. We appreciate the excellent work of the technical support staff in Berlin, Durham, Hamburg, Heidelberg, Palaiseau, Paris, Saclay, and in Namibia in the construction and operation of the equipment.

- P. Vincent, et al., Performance of the HESS cameras, in: Proceedings of the 28th ICRC, 2003.

- [2] C. L. Naumann, et al., New electronics for the Cherenkov Telescope Array (NECTAr), Nucl. Instrum. Methods Phys. Res. A 695 (2012) 44.

- [3] Yocto Project | Open Source embedded Linux build system, package metadata and SDK generator, https://www.yoctoproject.org/.

- [4] Apache thrift home, https://thrift.apache.org/.

- [5] Code connected zeromq, https://zeromq.org/.

- [6] Protocol buffers, https://developers.google.com/ protocol-buffers.